# Czech Technical University in Prague

Faculty of Electrical Engineering

Department of Control Engineering

# Diploma Thesis Message schedule verification for Profinet IRT

Author: Bc. Lukáš Halíř

2015

Czech Technical University in Prague Faculty of Electrical Engineering

Department of Control Engineering

## DIPLOMA THESIS ASSIGNMENT

#### Student: Bc. Lukáš Halíř

Study programme: Cybernetics and Robotics Specialisation: Systems and Control

### Title of Diploma Thesis: Message schedule verification for Profinet IRT

#### Guidelines:

1. Design a structure of a software tool to check the qualities of a message schedule for Profinet IRT.

2. Implement the tool and check the validity of the message schedules based on a given set of rules.

3. Study the usage of tool UPPAAL for model checking of time-critical systems.

4. Specify the state machine to control the forwarding of IRT messages in Profinet IO Device.

5. Implement the state machine in UPPAAL.

6. Create a model of a Profinet IRT network with a series of devices (line topology). Check if the behaviour of the network corresponds to a given message schedule.

#### Bibliography/Sources:

[1] Industrial communication networks - Fieldbus specifications - Part 5-10: Application layer service definition - Type 10 elements. IEC 61158-5-10 ed.3. 08/2014.

[2] Industrial communication networks - Fieldbus specifications - Part 6-10: Application layer protocol specification - Type 10 elements. IEC 61158-6-10 ed.3. 08/2014.

[3] Behrmann, G., David, A., Larsen, K.G. A Tutorial on Uppaal 4.0. 2006.

Diploma Thesis Supervisor: Ing. Pavel Burget, Ph.D.

Valid until the summer semester 2015/2016

prof. Ing. Pavel Ripka, CSc. Dean

Prague, February 20, 2015

# Prohlášení

Prohlašují, že jsem předloženou práci vypracoval samostatně a že jsem uvedl veškeré použité informační zdroje v souladu s Metodickým pokynem o dodržování etických principů při přípravě vysokoškolských závěrečných prací.

V Praze, dne. 11 5 2015

Par

Podpis

# Acknowledgment

At this place I would like to thank my supervisor Pavel Burget for his advices and comments on my work. Also thanks to Ondřej Fiala who helped me with various issues I have encountered during the work on this thesis. Last but not least, thanks to my family and everybody who supported me during my studies.

## Abstract

This thesis deals with verification of message schedules in Profinet IRT networks. For the verification two approaches were implemented and described in this thesis.

First approach is to verify the schedule by static check with given set of rules. A test tool with verification rules was implemented in this thesis and several schedules were verified.

In the second approach a model of Profinet network was created and parametrized by the schedule. The model was created in Uppaal software, which performs verification of timed automata systems according to specified requirements. Network with line topology was modeled and verified that it behaves according to the given schedule.

## Abstrakt

Tato práce se zabývá ověřováním plánu zpráv v sítích Profinet IRT. Pro ověřování byly v této práci implementovány a popsány dva přístupy.

Prvním z přístupů je oveření plánu statickou kontrolou jeho parametrů podle zadaných pravidel. V této práci byl implementován testovací nástroj se zadanými pravidly a s jeho pomocí bylo ověřeno několik plánů.

V druhém přístupu byl vytvořen model sítě Profinet a byl parametrizován zadaným plánem. Model byl vytvořen v programu Uppaal, který podporuje verifikaci časovaných stavových automatů podle zadaných požadavků. Byla namodelována síť s liniovou topologií a bylo ověřeno její chování podle plánu.

## Contents

| 1        | Intro                                                       | oduction                                                                             | 1                                    |

|----------|-------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------|

| <b>2</b> | Prof                                                        | inet IRT                                                                             | <b>2</b>                             |

| 2.1      | $\mathbf{Sch}\mathbf{\epsilon}$                             | eduling of communication                                                             | <b>2</b>                             |

| 2.2      | $\mathbf{Mes}$                                              | sage format                                                                          | 3                                    |

| 2.3      | Mes<br>2.3.1<br>2.3.2                                       | sage forwarding<br>Absolute forwarder                                                | <b>3</b><br>3<br>4                   |

| 3        | Test                                                        | tool                                                                                 | 5                                    |

| 3.1      | $\mathbf{Desi}$                                             | gn                                                                                   | 5                                    |

| 3.2      | Inpu                                                        | its                                                                                  | 6                                    |

| 0.2      | 3.2.1<br>3.2.2<br>3.2.3<br>3.2.4                            | Scheduling Input and Output                                                          | 6<br>6<br>6<br>7                     |

| 3.3      | Mod                                                         |                                                                                      | 8                                    |

|          | 3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7 | Configuration                                                                        | 8<br>9<br>10<br>10<br>11<br>11<br>12 |

| 3.4      | Pars                                                        | sers                                                                                 | 13                                   |

|          | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5                   | XmlParser                                                                            | 13<br>13<br>13<br>13<br>14           |

| 3.5      |                                                             |                                                                                      | 14                                   |

|          | 3.5.1<br>3.5.2<br>3.5.3<br>3.5.4                            | Class Test          Example test implementation          Test suite          Results | 15<br>16<br>17<br>17                 |

| 3.6      |                                                             |                                                                                      | 18                                   |

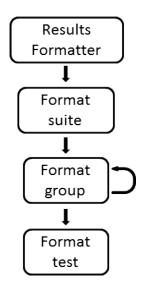

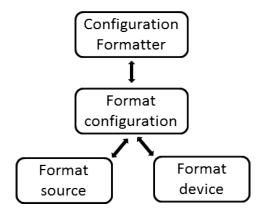

|          | $\begin{array}{c} 3.6.1 \\ 3.6.2 \end{array}$               | Formatting of the results                                                            | 18<br>18                             |

| 3.7      | Out                                                         | put                                                                                  | 19                                   |

| 3.8      | API                                                         |                                                                                      | 20                                   |

| 3.9      | Com                                                         | nmand Line Interface                                                                 | 20                                   |

| 3.1 | 3.10.1                                                                                      | $\operatorname{Confi}$                                  | User Interface<br>guration dialog                                                                                                                                                         |                                        |

|-----|---------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 3.1 | 1 Veri                                                                                      | ficatio                                                 | on of message schedules                                                                                                                                                                   | 22                                     |

| 4   | Upp                                                                                         | aal                                                     |                                                                                                                                                                                           | <b>24</b>                              |

| 4.1 | <b>Intr</b><br>4.1.1<br>4.1.2                                                               | State                                                   | ion to Uppaal<br>machines                                                                                                                                                                 |                                        |

| 4.2 | <b>IRT</b><br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9 | Frame<br>Overv<br>Demu<br>Bridg<br>Red H<br>Queu<br>Mux | ch         h parameters         e definition                                                                                                                                              | 27<br>27<br>27<br>28<br>29<br>30<br>30 |

| 4.3 | Netv<br>4.3.1<br>4.3.2                                                                      | Link<br>Verifi                                          | cation rules for message schedule                                                                                                                                                         |                                        |

| 4.4 | $\mathbf{Res}$                                                                              | ilts of                                                 | f network verification                                                                                                                                                                    | 35                                     |

| 4.5 | <b>Isoc</b><br>4.5.1<br>4.5.2<br>4.5.3<br>4.5.4<br>4.5.5<br>4.5.6<br>4.5.7                  | Defin<br>Exter<br>Contr<br>Isom<br>Isom<br>Devic        | us application         ition of isochronous application         nding switch to multiple cycles         coller         In         Out         e         cation of isochronous application | 38<br>38<br>39<br>39<br>40             |

| 4.6 | Resu                                                                                        | ilts of                                                 | f isochronous application verification                                                                                                                                                    | 41                                     |

| 5   | Con                                                                                         | clusio                                                  | on                                                                                                                                                                                        | 42                                     |

| Ap  | pendix                                                                                      | κA                                                      | List of implemented tests                                                                                                                                                                 | 44                                     |

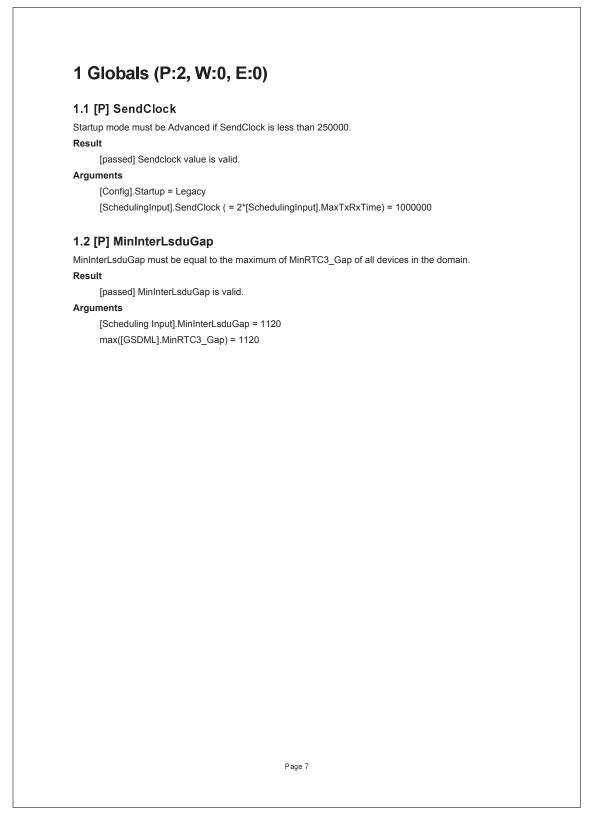

| Ap  | pendiz                                                                                      | ĸВ                                                      | Example of PDF report                                                                                                                                                                     | 47                                     |

| Ap  | pendiz                                                                                      | c C                                                     | Network verification                                                                                                                                                                      | 48                                     |

| Ap  | pendiz                                                                                      | c D                                                     | Verification of isochronous application                                                                                                                                                   | 50                                     |

| Ар  | pendix                                                                                      | κE                                                      | Content of attached CD                                                                                                                                                                    | 51                                     |

## List of Figures

| 1  | Profinet IRT message                               |

|----|----------------------------------------------------|

| 2  | Profinet IRT message for fast forwarding           |

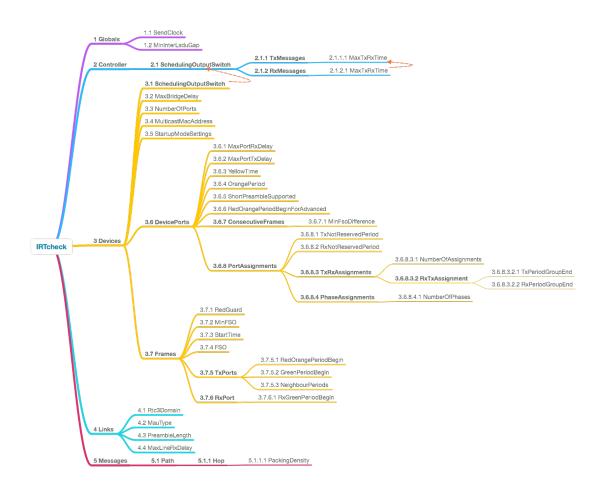

| 3  | Design of the library                              |

| 4  | Model of the configuration file                    |

| 5  | Model of the input for the scheduler 9             |

| 6  | Model of the output of the scheduler               |

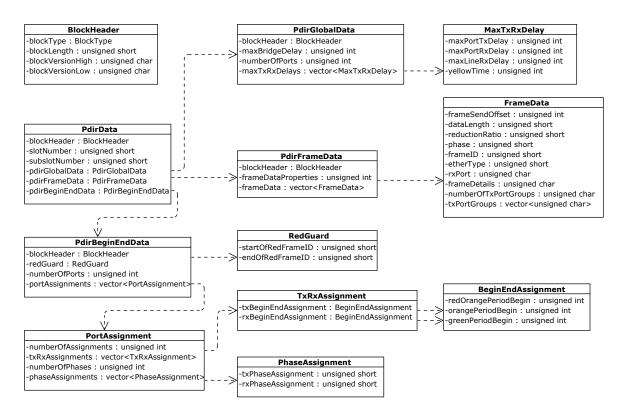

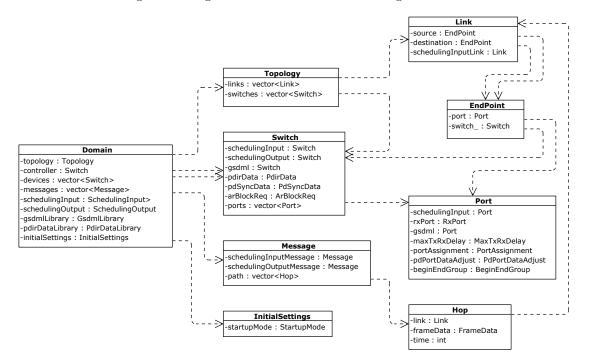

| 7  | Model of data record PDIRData 11                   |

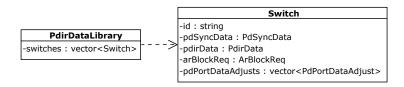

| 8  | Model of the data records library                  |

| 9  | Model of the GSDML files                           |

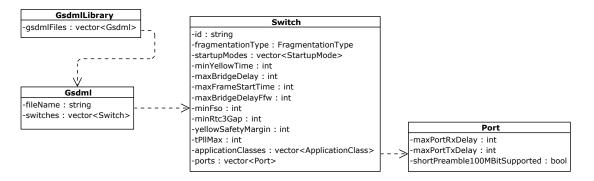

| 10 | Model of the whole network                         |

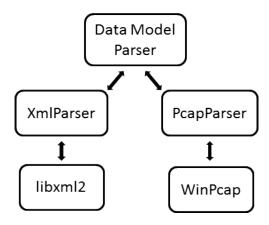

| 11 | Wrappers for third party libraries                 |

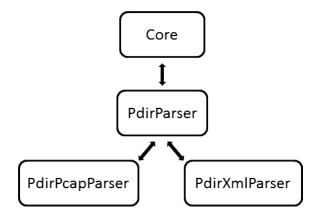

| 12 | Integration of parsers into the library            |

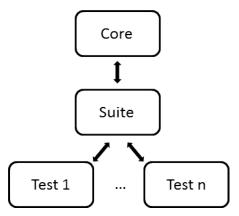

| 13 | Structure of the suite                             |

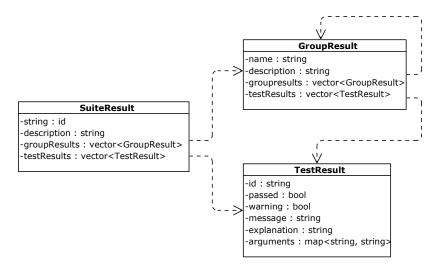

| 14 | Structure of test results                          |

| 15 | Results formatter                                  |

| 16 | Configuration formatter                            |

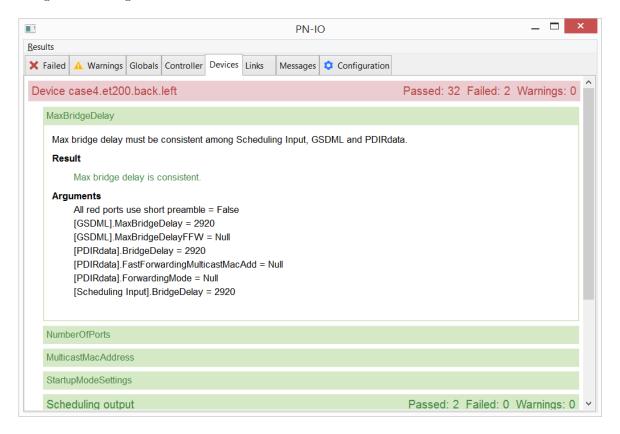

| 17 | Configuration dialog                               |

| 18 | Results view                                       |

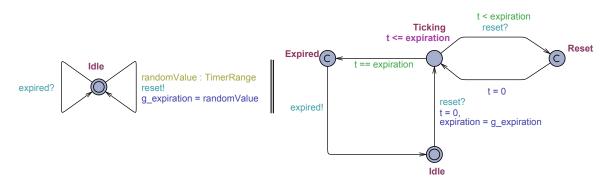

| 19 | Example of Uppaal state machines                   |

| 20 | Interconnection of state machines                  |

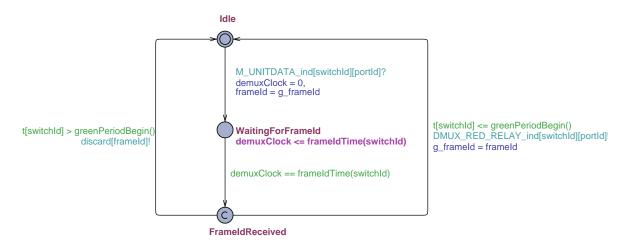

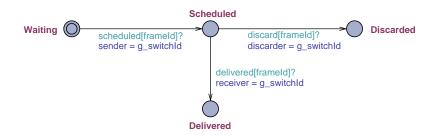

| 21 | Demux state machine                                |

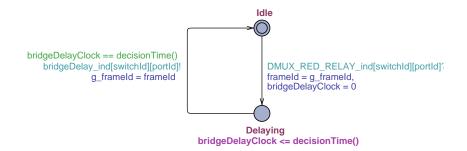

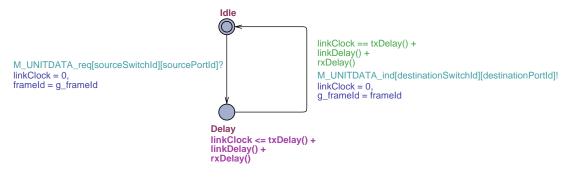

| 22 | Bridge Delay state machine                         |

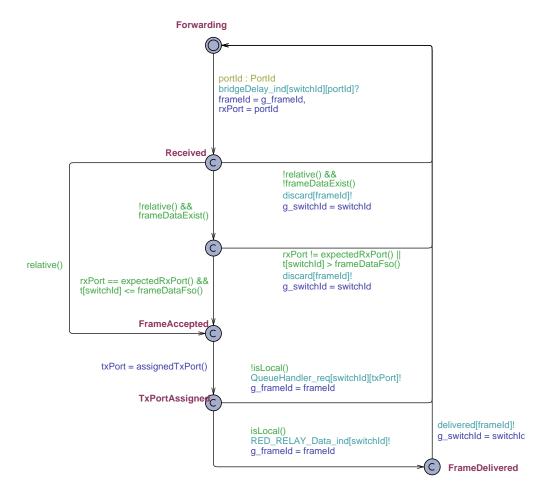

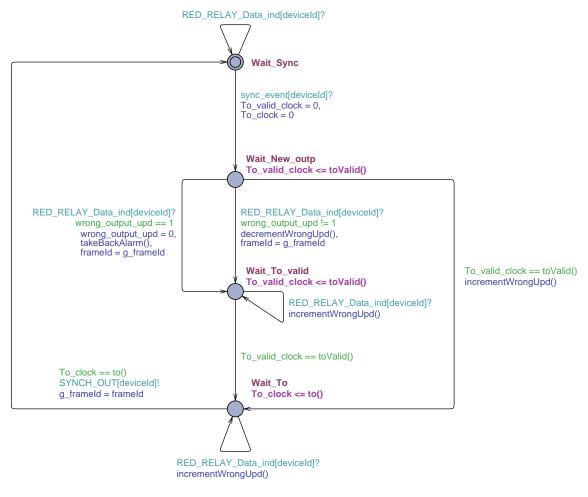

| 23 | Red Relay state machine                            |

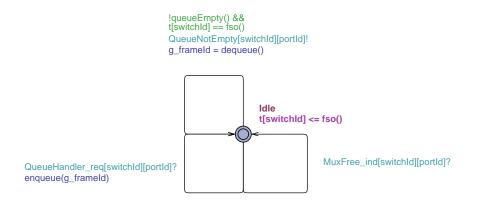

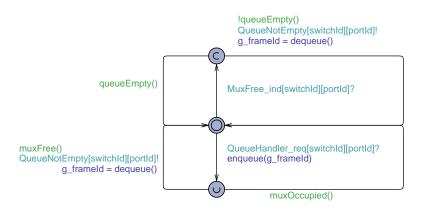

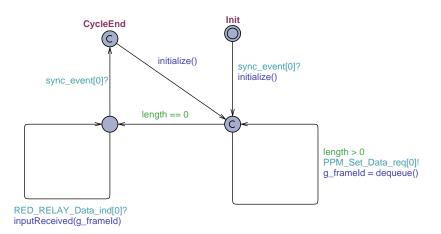

| 24 | Queue Handler state machine for absolute forwarder |

| 25 | Queue handler state machine for relative forwarder |

| 26 | Mux state machine                                  |

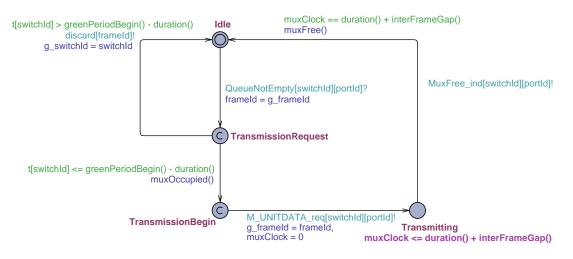

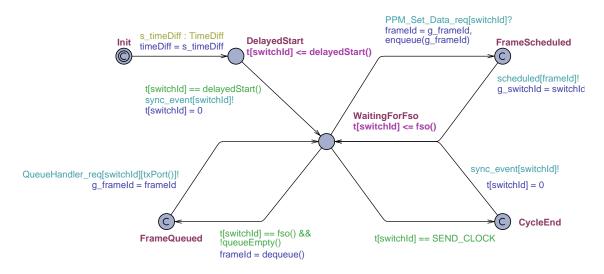

| 27 | Scheduler state machine                            |

| 28 | Link state machine                                 |

| 29 | Observer of the network behaviour                  |

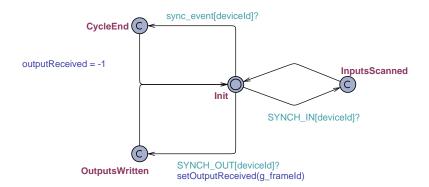

| 30 | Application state machine                          |

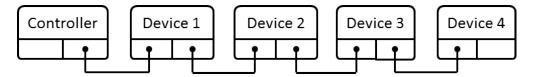

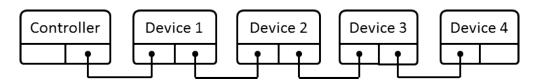

| 31 | Topology of the network                            |

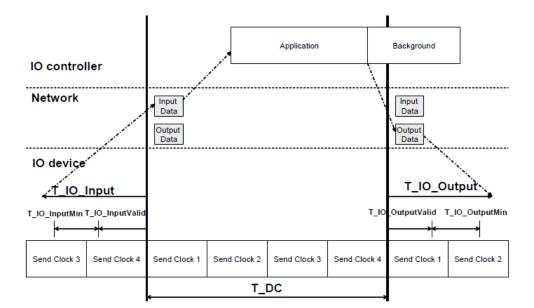

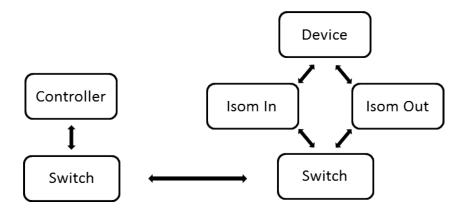

| 32 | Isochronous application                            |

| 33 | Isochronous application structure                  |

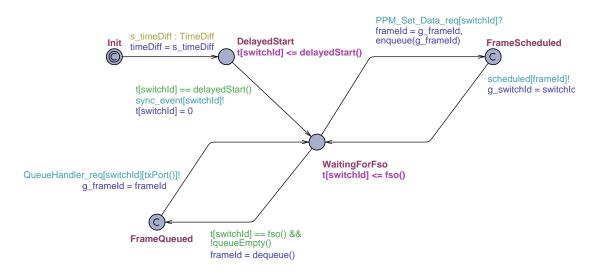

| 34 | Extended Scheduler state machine                   |

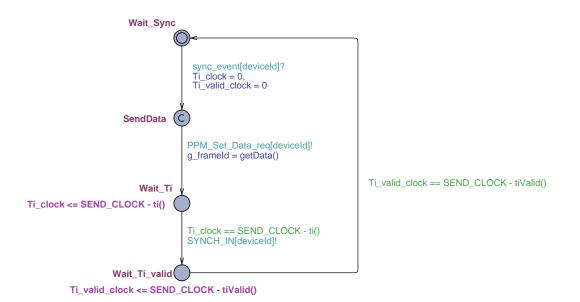

| 35 | Controller state machine                           |

| 36 | Isom In state machine                              |

| 37 | Isom Out state machine                             |

| 38 | Device state machine                               |

| 39 | Structure of implemented tests 44                  |

| 40 | Example of PDF report                              |

| 41 | Topology of the network                            |

## List of Tables

| 1                                       | List of available parsers for individual input files.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8                                      |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 2                                       | Mapping of attributes from device configuration to other models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14                                     |

| 3                                       | Interpretation of TestResult attributes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                     |

| 4                                       | Uppaal requirement specification language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25                                     |

| 5                                       | Structure Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26                                     |

| 6                                       | Structure Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26                                     |

| 7                                       | Structure FrameData                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 26                                     |

| 8                                       | Global constants of the network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 26                                     |

| 9                                       | Structure Frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27                                     |

| 10                                      | Structure Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32                                     |

| 11                                      | Structure Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 37                                     |

| 12                                      | Structure Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 37                                     |

| 13                                      | Global constants of isochronous application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 37                                     |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 01                                     |

| 14                                      | Switch parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 48                                     |

| $\begin{array}{c} 14 \\ 15 \end{array}$ | Switch parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                        |

|                                         | Switch parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 48                                     |

| 15                                      | Switch parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $\frac{48}{48}$                        |

| $\frac{15}{16}$                         | Switch parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 48<br>48<br>48                         |

| $15 \\ 16 \\ 17$                        | Switch parameters       Switch parameters         Switch parameters       Port parameters         Forwarding rules       Frame definitions         Link definitions       Support Sup | $48 \\ 48 \\ 48 \\ 49$                 |

| 15<br>16<br>17<br>18                    | Switch parameters       Switch parameters         Port parameters       Forwarding rules         Forwarding rules       Frame definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $48 \\ 48 \\ 48 \\ 49 \\ 49 \\ 49$     |

| 15<br>16<br>17<br>18<br>19              | Switch parameters       Switch parameters         Switch parameters       Port parameters         Forwarding rules       Frame definitions         Link definitions       Support Sup | 48<br>48<br>49<br>49<br>49             |

| 15<br>16<br>17<br>18<br>19<br>20        | Switch parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 48<br>48<br>49<br>49<br>49<br>49       |

| 15<br>16<br>17<br>18<br>19<br>20<br>21  | Switch parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 48<br>48<br>49<br>49<br>49<br>49<br>50 |

## Listings

| 1  | PDIRdata XML format                                             |

|----|-----------------------------------------------------------------|

| 2  | Configuration XML format                                        |

| 3  | Constructor                                                     |

| 4  | Test rule implementation 16                                     |

| 5  | An example implementation of the functions in a test            |

| 6  | Output XML with results                                         |

| 7  | Main method of the public API                                   |

| 8  | Methods to run tests and to return the resulting data structure |

| 9  | Methods format data structures into XML strings                 |

| 10 | Method to get data model of the configuration file              |

| 11 | Delivery of message                                             |

| 12 | Sender of the message                                           |

| 13 | Receiver of the message                                         |

| 14 | Timing of messages for absolute forwarder                       |

| 15 | Timing of messages for relative forwarder                       |

| 16 | Path of messages for absolute forwarder 35                      |

| 17 | Path of messages for relative forwarder                         |

| 18 | Inputs received                                                 |

| 19 | Outputs received                                                |

| 20 | Output timing                                                   |

| 21 | Input timing                                                    |

|    |                                                                 |

## Chapter 1 Introduction

This thesis deals with verification of message schedules for Profinet IRT networks. The schedule is crucial for real time applications and if it is miscalculated it might lead to loss of data in the network. The scheduling is a very complex task because a lot of constraints are given by physical limits of used devices and at the same time the schedule should often be optimized to minimize the time needed to propagate the information through the network.

Many approaches exist in the scheduling of the communication and each of them might provide different results. The results should be verified if they really meet the criteria given by the real environment. First idea could be to build a network from real hardware and to observe if it really behaves according to the schedule. Building a network can be a resource demanding task and the costs easily overcome the benefit which is only the verification of the schedule.

The goal of this thesis is to develop software methods to allow verification of message schedules. Two approaches of the verification are presented. The first one is a test tool which performs a static check of schedules. The requirements on the schedule are specified as the test rules and the tool evaluates if the schedule meets all the requirements by verification that no rules are violated.

The second approach is to create a model of the network which can be parametrized by a message schedule. A verification engine can be used to evaluate if the network is capable of following the message schedule.

The thesis is divided into five chapters. The second chapter (Profinet IRT) briefly introduces the reader into Profinet IRT networks and summarizes the knowledge necessary for understanding the following chapters. The third chapter (Test tool) presents how a test tool for the schedule verification was designed and implemented. The internal structure of the tool is described there as well as its user interfaces. Chapter Uppaal describes modeling of Profinet network in Uppaal software and how it was used to verify a message schedule. The last chapter summarizes the results of the thesis and suggests possible future extensions of implemented methods.

## Chapter 2 Profinet IRT

Profinet IRT (Isochronous Real Time) is a communication concept based on Ethernet. It was designed for a cyclic data exchange in real time applications which demand fast response times. A typical application is a synchronization of drives in fast processes like milling or printing machines where the drives of individual axes must perform synchronized movements with high precision.

Due to the demands of applications on fast response times, very little data loss in the network should occur. However, Ethernet is not a deterministic environment and neither data delivery nor delivery time is guaranteed. Any message can be delayed at a switch or even dropped as a result of its overload. Therefore Profinet IRT defines extension of Ethernet for real time networks which enforces its deterministic behaviour.

All devices in Profinet networks contain the extended Ethernet switch to communicate with the rest of the network. The switch provides communication services for the transfer and reception of data. The services are used by an application running on the device, which can be a controller or an I/O device.

First of all Profinet IRT introduces mechanisms to synchronize the clocks of individual switches to the same rate. When the clocks are synchronized the communication cycle with a certain length is defined. This cycle is divided into two main phases, red and green. The red phase is reserved for the deterministic real time communication and the green phase is left for other traffic. From this division it can be seen that the real time application can co-exist with non-real time traffic on the same network.

To avoid random drops of frames in the red phase the communication is scheduled with high precision. The schedule ensures that no collisions of the frames occur and every frame is delivered to its receiver at deterministic time.

## 2.1 Scheduling of communication

The schedule of the communication is calculated in an engineering tool where the network is planned before the data exchange happens. The scheduling algorithm must be aware of the network topology and properties of switches. The properties include propagation delays caused by the finite speed of their operation and they must be taken into account during the planning phase so the schedule is created in a way that the switches are able to follow it. These properties are described in GSDML (General Station Device Markup Language) files [4]. Together with the topology, the algorithm must know what messages are to be sent through the network and their length. The messages are identified by a unique ID which is used by the switches during the forwarding of the frames. The format of the messages is described in section 2.2.

The output of the scheduler is a list of forwarding rules for individual switches in the network. Each rule contains ID of the message to which it relates and the ports where the message is received and transmitted. This combination creates a path of the message through the network. Together with the path, timing information is provided to tell the switch at which time from the beginning of the cycle the transmission should happen. This time is called Frame Send Offset (FSO). Frame Send Offset is defined as the time point when the transmission of the first byte of Ethernet header should start at underlying physical layer. Precise definition of this time point is given in IRT Engineering Guideline [5]. The behaviour of the switches with relation to the calculated schedule is described in section 2.3.

There might be lots of scheduling algorithms with various formats of their output, thus Profinet provides definitions of data records in document [1]. These data records are loaded into the switches during the start-up of the network and determine the behaviour of the switches. For the message schedule verification, data record PDIRData is very interesting because it contains the forwarding rules and the boundaries of the red phase calculated by the scheduler.

### 2.2 Message format

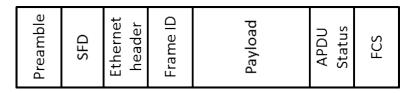

Messages are sent in standard Ethernet frames with the structure shown in figure 1.

Figure 1: Profinet IRT message

Ethernet frame starts with Preamble, Start Frame Delimiter (SFD) and Ethernet header. It is followed by Frame ID, payload and status of the frame (APDU Status). At the end of the message there is Ethernet Frame Check Sequence (FCS). Frame ID is encoded in the first two octets after Ethernet header. To increase the throughput of the network switches use the cut through mechanism. This approach allows forwarding of a frame while it is still being received. In IRT switches the forwarding is based on Frame ID and once it is received the frame can be forwarded.

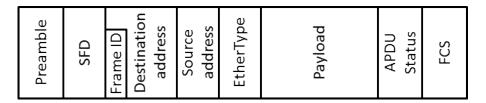

To further reduce the propagation delay caused by a switch, Frame ID can be encoded in the first two octets of the destination address in Ethernet header. This approach is called fast forwarding (FFW) and the format of the message is shown in figure 2. With this approach the frame can be forwarded after the first two octets of Ethernet header are received.

There is one more option to reduce the propagation delay. Instead of the long Ethernet preamble (7 octets) the short one can be used (1 octet).

Figure 2: Profinet IRT message for fast forwarding

## 2.3 Message forwarding

From the switch point of view the messages can be divided into three categories:

- injected

- forwarded

- consumed

Injected messages are not received on any port, but they are injected to the network by the switch. Opposite of this case are received messages, they are not forwarded to any port, they are delivered to the application running on the switch. Forwarded messages are none of the previous, they are received on a port and forwarded to another one according to PDIRData.

IRT switches can be divided into the two types, absolute and relative. They are described below.

#### 2.3.1 Absolute forwarder

Absolute forwarders have the forwarding information in PDIRData for all three categories. When a message is received its Frame ID is found in PDIRData and it is forwarded according to it. If the Frame ID is not found, the message is discarded. Sending of messages is synchronized with local the clock and they are sent according to their FSO.

Absolute forwarders contain PDIRData for the forwarded frames and thus they can have more than two ports and complex topologies can be built with them.

### 2.3.2 Relative forwarder

Relative forwarders do not contain forwarded frames in their PDIRData and they can have only two ports. Messages received on one port are forwarded to the other port. No timing information is available either and FSO is reconstructed from the time when they are received. Sending of the messages is not synchronized with the local clock and they are sent out at the time relative to their reception.

The relative forwarders can achieve better performance than absolute forwarders with respect to the time a message spends in the switch, but they are limited with two ports.

## Chapter 3 Test tool

This chapter describes the design and the implementation of the test tool which verifies the message schedule. The message schedule is stored in PDIRData of individual switches and it is tested to verify that the schedule is valid. As it was described in section 2.1, PDIRData are created from the message schedule calculated by a scheduling algorithm. The tool tests if the transformation was done correctly by comparison of PDIRData with the input and output of the scheduler. The schedule itself is tested if it does not violate equations presented in IRT Engineering Guideline [5]. The equations were transformed into the test rules and the test tool evaluates them to find out if they are violated or not.

The tool provides a graphical interface where the results can be clearly displayed. They can also be saved to an XML file for further processing by another application or they can be printed into a PDF report.

To perform the tests it is necessary to specify the sources of data and additional information. The tool provides a form where the necessary inputs are configured and the configuration can be saved to an XML file and later loaded back. Formats of the input data can vary with their version or an application which generated them. Multiple formats of the input files are supported to enable usage of the tool to as many users as possible and the tool was designed to support possible future extensions of new file formats.

The tool was implemented in C++ programming language. Its implementation was successfully tested on Windows platforms. However, the implementation uses only libraries which are portable between most commonly used platforms and it can be easily ported to Linux or Mac platforms without large changes in the source code.

## 3.1 Design

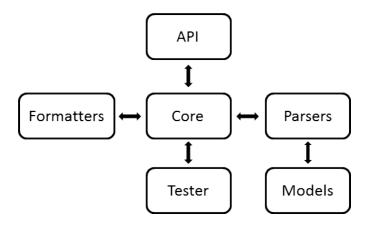

The application was required to have both Graphical User Interface (GUI) and Command-line Interface (CLI). It leads to the design where the core functionality of testing was extracted into a testing library and two applications were implemented as an interface for it. The applications are described in sections 3.9 and 3.10 and they use public Application Programming Interface (API) to perform tests or utilize another functionality of the core. The public API, described in section 3.8, can be also used to integrate the library into another application.

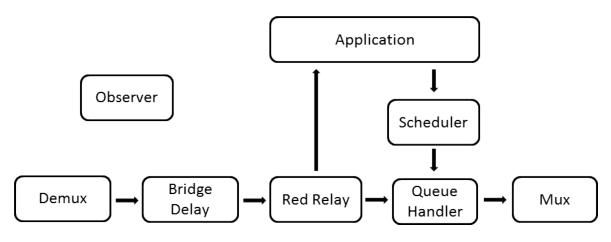

The design of the library is shown in figure 3. Its API is called from applications and the requests are passed to the core. The core controls the flow of the program execution and uses individual modules to achieve the requested functionality.

Figure 3: Design of the library

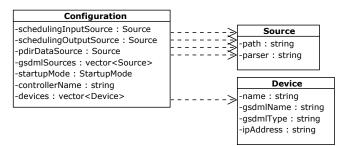

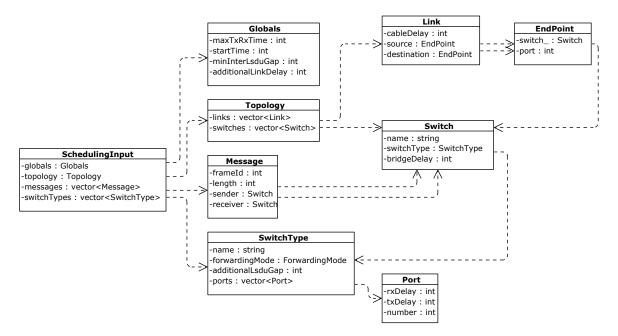

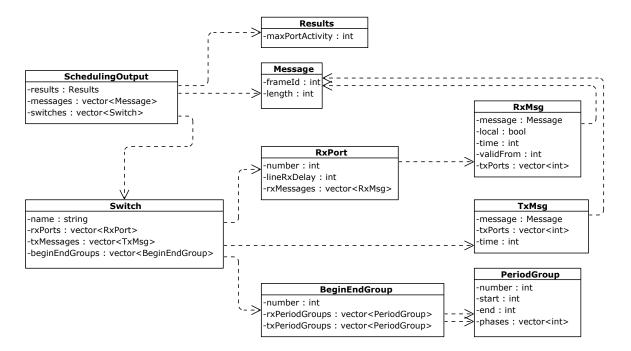

To perform the testing, several inputs must be provided for the library. The inputs are data records for individual switches, input and output of the scheduler and GSDML files describing the switches. Details about individual inputs are given in section 3.2. Every input might be stored in various file formats of different versions. For this reason it was decided to represent each input with a data model in module Models. Individual data models are described in section 3.3.

The data models are created from input files by parsers in module Parsers. They deal with the specifics of the format where the data are stored, and extract them to create the corresponding data models. With this approach the data models are independent of the file format. If a new format of the input data should be supported in the future, it will be sufficient to implement a new parser which will fill the data model and the rest of the library will remain unaffected. The parsers are described in section 3.4.

The implementation of the test rules and their organization was implemented in module Tester, described in section 3.5. The tests usually involve checks of values across the inputs, thus a new data model was designed to perform the testing on. This model is created from data models of individual inputs based on the configuration which is also one of the inputs of the application.

The outputs of the library are the results of the tests. They can be returned as a data structure for immediate processing or as an XML file. For the conversion of the data structures into XML files, module Formatters was designed. Inside this module the results can be formatted into the output format described in section 3.7. Detailed description of this module can be found in section 3.6.

### 3.2 Inputs

Description of individual inputs for the test tool is given in this section. There are several files needed for the verification of a message schedule, input and output of the scheduler, device descriptions in GSDML and a file containing the data records. For storage of the test configuration a configuration file was designed.

#### 3.2.1 Scheduling Input and Output