### **Master Thesis**

Czech Technical University in Prague

Faculty of Electrical Engineering Department of Control Engineering

# Time-predictable GPU execution

Flavio Kreiliger

Supervisor: Ing. Joel Matějka Field of study: Cybernetics and Robotics May 2019

# MASTER'S THESIS ASSIGNMENT

### I. Personal and study details

| Student's name:      | Kreiliger Flavio                       | Personal ID number: | 473095 |

|----------------------|----------------------------------------|---------------------|--------|

| Faculty / Institute: | Faculty of Electrical Engineering      |                     |        |

| Department / Instit  | ute: Department of Control Engineering |                     |        |

| Study program:       | Cybernetics and Robotics               |                     |        |

| Branch of study:     | Cybernetics and Robotics               |                     |        |

#### II. Master's thesis details

Master's thesis title in English:

**Time-predictable GPU execution**

Master's thesis title in Czech:

#### Časově deterministické vykonávání kódu na GPU

#### Guidelines:

1. Make yourself familiar with ongoing efforts and results of making the GPU code execution predictable i.e. suitable for hard real-time embedded applications.

2. Evaluate existing approaches such as PREM-compiler and GPUguard on NVIDIA Tegra X2 SoC.

3. Investigate sources of unpredictability of GPU execution such as cache contention, memory bus contention, GPU scheduling and operating system scheduling.

4. Propose and implement a mechanism for time-triggered scheduling of GPU execution with the goal of reducing timing unpredictability.

5. Document and test all the developed techniques

#### Bibliography / sources:

[1] J. Bakita, N. Otterness, J. Anderson, and F.D. Smith, "Scaling Up: The Validation of Empirically Derived Scheduling Rules on NVIDIA GPUs", Proceedings of the 14th Annual Workshop on Operating Systems Platforms for Embedded Real-Time Applications, pp. 49-54, July 2018.

[2] Matejka, Joel & Forsberg, Björn & Sojka, Michal & Sucha, Premysl & Benini, Luca & Marongiu, Andrea & Hanzálek, Zdeněk. (2018). Combining PREM Compilation and Static Scheduling for High-Performance and Predictable MPSoC Execution. Parallel Computing. 10.1016/j.parco.2018.11.002.

[3] B. Forsberg, A. Marongiu and L. Benini, 'GPUguard: Towards supporting a predictable execution model for heterogeneous SoC,' Design, Automation & Test in Europe Conference & Exhibition (DATE), 2017, Lausanne, 2017, pp. 318-321.

[4] NVIDIA: CUDA C PROGRAMMING GUIDE, v10.0.130, Oct. 31, 2018.

Name and workplace of master's thesis supervisor:

#### Ing. Joel Matějka, Department of Control Engineering, FEE

Name and workplace of second master's thesis supervisor or consultant:

Date of master's thesis assignment: 06.02.2019

Deadline for master's thesis submission: 24.05.2019

Assignment valid until: 20.09.2020

Ing. Joel Matějka Supervisor's signature prof. Ing. Michael Šebek, DrSc. Head of department's signature prof. Ing. Pavel Ripka, CSc. Dean's signature

# III. Assignment receipt

The student acknowledges that the master's thesis is an individual work. The student must produce his thesis without the assistance of others, with the exception of provided consultations. Within the master's thesis, the author must state the names of consultants and include a list of references.

Date of assignment receipt

Student's signature

# **Acknowledgements**

First, I would like to thank my supervisor Joel Matějka for his immense support, helpful advice, and productive discussions.

Further, I express my thanks to Michal Sojka, for contributing with his deep knowledge during our weekly meetings.

I would like to express my gratitude to Professor Zdeněk Hanzálek for the opportunity to write my thesis in his group.

Their help and support during the writing process of the paper "Experiments for Predictable Execution of GPU Kernels" made it possible to publish parts of this thesis to the OSPERT19 conference.

Finally, I would like to say thank you to my parents for supporting me during my studies.

# Declaration

I hereby declare that the submitted thesis is exclusively my own work and that I have listed all used information sources in accordance with the Methodological Guideline on Ethical Principles for College Final Work Preparation.

Prague, 24. May 2019

# Abstract

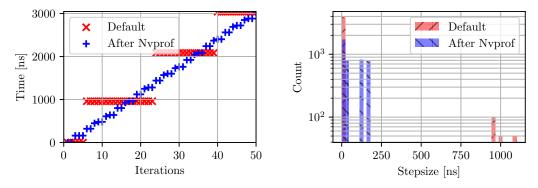

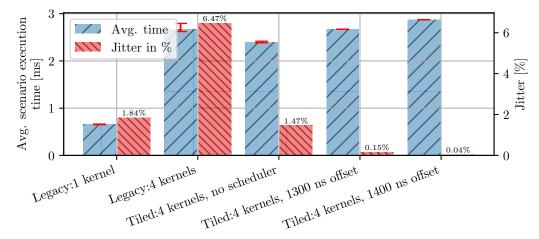

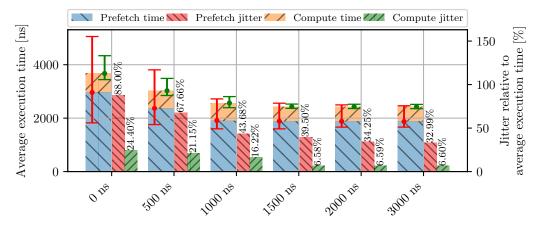

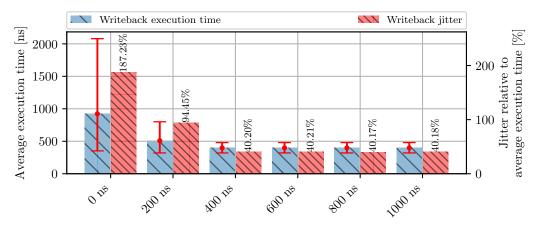

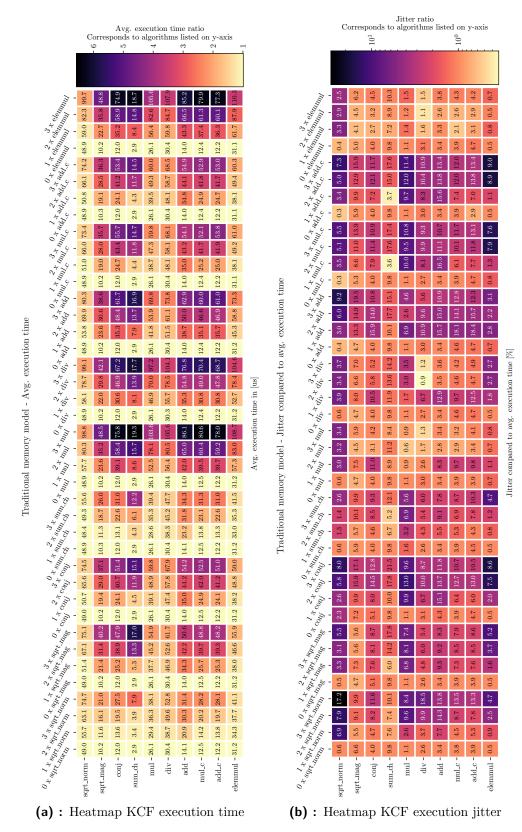

In this thesis, we evaluate the interference between multiple GPU (Graphics processing unit) kernels running in parallel based on artificial random and sequential walks, the 2D Convolution benchmark provided by polybench and the KCF (Kernelized Correlation Filter) tracker implemented by Vít Karafiát and Michal Sojka. To achieve a reduction of the interference between the running kernels and to reduce the resulting execution jitter, we used a time-triggered execution on the GPU. To enable the synchronization, we assessed two synchronization mechanisms available on Tegra X2 platform: one based on zerocopy memory and one based on the globaltimer. We found that the NVIDIA profiler (nvprof) reconfigures the resolution of globaltimer from 1 µs to 160 ns. With this resolution, we were able to reduce the execution time jitter of a tiled 2D convolution kernel from 6.47% to 0.15%while maintaining the same average execution time by use of a time-triggered GPU execution.

**Keywords:** predictable execution, gpu, nvidia, tx2, prem, interference

Supervisor: Ing. Joel Matějka

# Contents

| 1 Introduction                            | 1              |

|-------------------------------------------|----------------|

| 2 Background                              | 3              |

| 2.1 Real time applications                | 3              |

| 2.1.1 WCET                                | 4              |

| 2.1.2 Predicatbility problems in          |                |

| COTS                                      | 4              |

| 2.2 PREM                                  | 5              |

| 2.2.1 Concept                             | 6              |

| 2.3 GPU introduction                      | $\overline{7}$ |

| 2.3.1 GPU on the Jetson TX2 $\ldots$      | 8              |

| 2.4 CUDA                                  | 12             |

| 2.4.1 Programming model                   | 12             |

| 2.4.2 Memory model                        | 13             |

| 2.4.3 Coalescent access                   | 17             |

| 2.5 OpenMP offloading                     | 18             |

| 2.5.1 Offloading kernels                  | 19             |

| 2.6 GPU scheduling on the TX2 $\dots$     | 22             |

| 2.7 Related work                          | 23             |

| 2.7.1 GPU-GUARD                           | 24             |

| 2.7.2 PREM-Synchronization with           |                |

| GPUguard                                  | 26             |

| 2.7.3 Mem-guard                           | 27             |

| 3 Methodology                             | 29             |

| 3.1 Platform characterization             | 29             |

| 3.1.1 SASS                                | 30             |

| 3.1.2 Measurement overhead                | 32             |

| 3.1.3 Cache analysis                      | 32             |

| 3.1.4 Interference between threads        | 33             |

| 3.1.5 Interference between kernels .      | 34             |

| 3.1.6 Interference CPU to GPU             | 34             |

| 3.2 Time-triggered GPU                    | 35             |

| $3.2.1~{\rm Synchronization}$ mechanism . | 35             |

| 3.2.2 Convolution benchmark               | 36             |

| 3.2.3 Reduction of intra-GPU              |                |

| interference                              | 36             |

| 3.2.4 Tiling                              | 36             |

| $3.2.5$ Tile scheduling $\ldots$          | 37             |

| 3.3 KCF-Tracker interference analysis     | 40             |

| 4 Experimental evaluation                 | 41             |

| 4.1 Kernel interference                   | 41             |

| 4.1.1 Cache analysis                      | 41             |

| 4.1.2 Walks - Multiple threads            | 42             |

| 4.1.3 Walks - Multiple kernel             | 43             |

| 4.1.4 CPU interference                    | 45             |

|                                           |                |

| B Bibliography                      | 63 |  |  |  |  |

|-------------------------------------|----|--|--|--|--|

| A Abbreviated terms                 | 61 |  |  |  |  |

| 5.1 Future work                     | 59 |  |  |  |  |

| 5 Conclusion                        | 59 |  |  |  |  |

| 4.4 Summary                         |    |  |  |  |  |

| 4.3 KCF-Tracker kernel interference | 56 |  |  |  |  |

| 4.2.4 Phase evaluation              | 52 |  |  |  |  |

| tiled 2D Convolution                | 49 |  |  |  |  |

| 4.2.3 Time triggered execution of   |    |  |  |  |  |

| 4.2.2 GPU timer granularity         | 48 |  |  |  |  |

| synchronization evaluation          | 48 |  |  |  |  |

| 4.2.1 Zero-copy memory              |    |  |  |  |  |

| GPU execution                       | 48 |  |  |  |  |

| 4.2 Experiments for time-triggered  |    |  |  |  |  |

# Figures Tables

| 2.1 Worst-Case Execution Time              | 4               |

|--------------------------------------------|-----------------|

| 2.2 Evolution of code size                 | 5               |

| 2.3 Predictable interval                   | 6               |

| 2.4 GPU rigid pipeline                     | 8               |

| 2.5 Graphics pipeline evolution $\ldots$ . | 9               |

| 2.6 CPU vs GPU performance                 | 10              |

| 2.7 GP100 Pascal micro-architecture        | 11              |

| 2.8 Diverged Warp execution                | 11              |

| 2.9 SM architecture TX2                    | 11              |

| 2.10 CUDA models                           | 13              |

| 2.11 Traditional memory model              | 15              |

| 2.12 TX2 block diagram                     | 16              |

| 2.13 Coalescent memory access $\ldots$     | 17              |

| 2.14 OpenMP model                          | 18              |

| 2.15 OpenMP parallel launch                | 21              |

| 2.16 OpenMP teams launch                   | 21              |

| 2.17 TX2 queue architecture                | 23              |

| 2.18 GPUguard architecture                 | 25              |

| 2.19 GPU-guard synchronization             | 26              |

| 2.21 MemGuard architecture                 | 28              |

|                                            | ~ .             |

| 3.1 Start elements of threads              | 34              |

| 3.2 2D Convolution tiling                  | 37              |

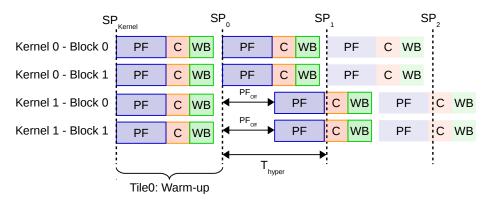

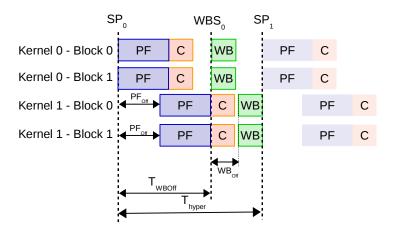

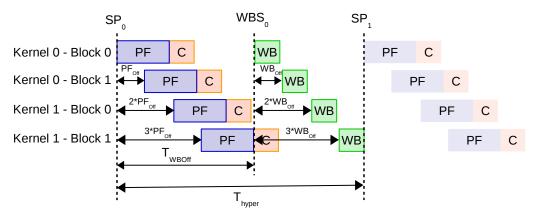

| 3.3 Tile scheduling – Kernel-wise          | 39              |

| 3.4 Tile scheduling – Block-wise           | 39              |

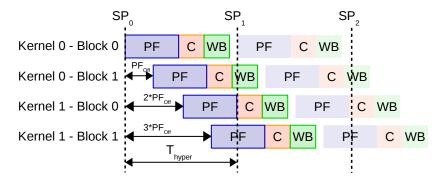

| 3.5 Phase scheduling – Kernel-wise .       | 39              |

| 3.6 Phase scheduling – Block-wise          | 40              |

| 4.1 Cache hierarchy                        | 42              |

| 4.2 Walks – Multiple threads               | 44              |

| 4.3 Walks – Multiple kernels               | $\overline{45}$ |

| 4.4 Sequential walks – CPU                 |                 |

| interference                               | 46              |

| 4.5 Cache hierarchy                        | 47              |

| 4.6 Globaltimer jitter                     | 49              |

| 4.7 Whole tiles scheduled                  | 50              |

| 4.8 Scheduling comparison                  | 52              |

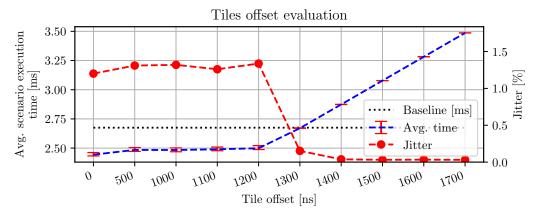

| 4.9 Tile offset evaluation                 | 53              |

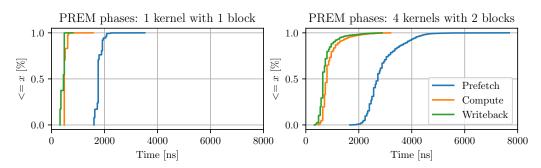

| 4.10 Phase CDF                             | 54              |

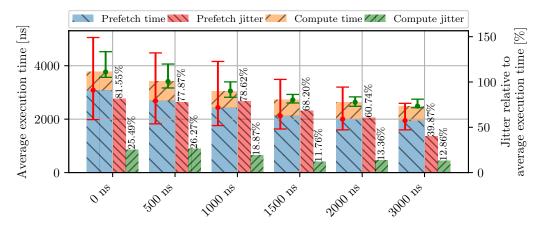

| 4.11 Prefetch and writeback shift          | 55              |

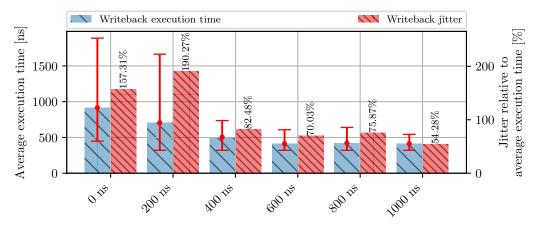

| 4.12 Writeback phase shift                 | 55              |

| 4.13 Prefetch and writeback shift –        |                 |

| Block-wise                                 | 56              |

| 4.14 Writeback phase shift –               |                 |

| Block-wise                                 | 56              |

| 4.15 KCF heat maps                         | 58              |

|                                            |                 |

| 2.1 Measured execution phases                                                             | 27 |

|-------------------------------------------------------------------------------------------|----|

| <ul><li>3.1 Technical specification of the TX2</li><li>3.2 Measurement overhead</li></ul> |    |

| 4.1 Scheduling comparison                                                                 | 53 |

# Chapter 1 Introduction

Autonomous machines such as self-driving cars will certainly be a part of our future. Nowadays, both industry and researchers work heavily on various aspects of those machines. One aspect that is still not satisfactorily addressed is how to ensure their safe operation. Those machines require vast computational power to process all the sensor data, and reason about them in real-time, but safety systems are traditionally implemented with slow, simple but reliable computing elements. In contrast to that, autonomous machines are powered with heterogeneous computing architectures, where a multi-core Central Processing Unit (CPU) is accompanied by one or more accelerators such as Graphics processing units (GPU)s or Fieldprogrammable gate arrays (FPGAs), often in the same chip. These are called Multi-Processor Systems-on-Chip (MPSoC).

While FPGAs can offer precise timing, GPUs seems to be more popular in these applications, perhaps due to their easier programmability. However, GPUs originate from industrial domains, where average-case performance was traditionally more important than real-time and safety guarantees. In this work, we use NVIDIA Tegra X2.

To reason about safety properties, the functional safety standard for road vehicles ISO 26262 defines the term "freedom from interference". Freedom from interference between software elements in the system allows those elements to be analyzed independently, simplifying the whole safety process. Elements are free from interference when certain faults, for example "incorrect allocation of execution time", are not present.

We believe (and safety standards agree) that time triggered scheduling gives stronger safety guarantees. One reason is that it is easier to control contention on shared hardware resources (caches, buses, memories) and thus control the inter-task interference. Our longer-term goal is to schedule execution on the whole MPSoC (CPUs and GPU) in time triggered manner. In our past work [1], we reduced interference between tasks on a multi-core CPU by time triggered scheduling.

Another reason for time triggered scheduling is that traditional synchronization schemes such as semaphores and spinlocks are more expensive on larger platforms. Therefore we aim to use time triggered scheduling within shorter time intervals and then occasionally (re)synchronize these intervals using traditional synchronization techniques.

#### 1. Introduction

Correct execution time allocation must be derived from the Worst case execution time (WCET) analysis. If the results of WCET analysis are too pessimistic, more time must be allocated and the computational power provided by the MPSoC is wasted and may not be sufficient for required autonomous operation.

In this thesis, we concentrate on the GPU execution only, and we try to characterize the interference between GPU kernels running in parallel and the resulting increase of their average execution time. Based on these findings, we want to show under which circumstances the resulting execution jitter is low or high.

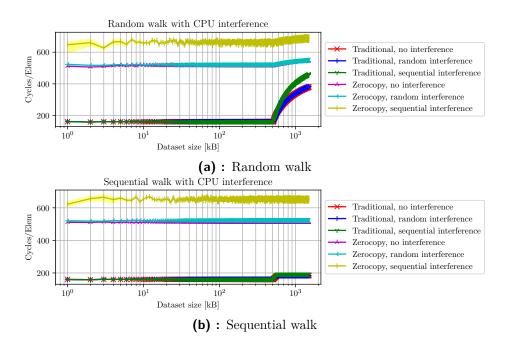

To describe the interference between GPU kernels, we analyze the interference between kernels performing sequential and random walks in parallel. Further, we evaluate how interference induced from the CPU affects the average element access times during those walks.

In a next step, we analyzed this contention with a less artificial kernel than the sequential and random walk kernels. We analyzed memory sensitivity of the available polybench [2] kernels and found the 2D Convolution an appropriate to show how the launch of multiple instances running in parallel influences the execution jitter.

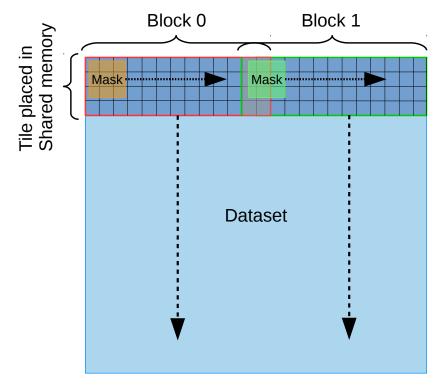

Later we reimplemented the 2D Convolution kernel to split the processed dataset into multiple tiles which fit into the GPUs shared memory. This change allowed us to break the tile processing into three phases: 1) prefetch data into shared memory, 2) perform the computation on the shared memory, and 3) write back the results from shared memory to global memory.

More specifically, we adopt the concept of Predictable Execution Model (PREM) proposed by Pellizzoni et al. [3], where computation is split into memory and compute phases, and these phases are scheduled to not interfere with each other. For example, by not running two memory phases in parallel.

To be able to synchronize the PREM phases, we assessed two synchronization mechanisms available on the Tegra X2 platform: One based on Zerocopy memory and one based on the globaltimer residing on the GPU.

Finally, we performed multiple experiments by scheduling the processed tiles and the PREM phases with different offset to determine how the reduced interference affects the resulting execution time and execution jitter.

To evaluate our findings on an application closer to reality, we measured the interference between the complex matrix operation kernels present in the Kernelized Correlation Filter (KCF) tracker [4] to understand which kernels interfere the most and where the reduced interference might provide the biggest benefits.

Parts of this thesis have been accepted as the paper *Experiments for Predictable Execution of GPU Kernels* by OSPERT19<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>https://ospert19.tudos.org/

# Chapter 2

Background

# 2.1 Real time applications

In many technical applications, such as process or engine control applications, it is compelling that the systems react in a given deadline. This might be less of a problem for temperature controlling applications, but for safety-critical systems, where serious harm as injuries, death or material damage can happen. The main task of such a system is to deliver the correct result of a job within a given deadline. This deadline can have an arbitrary length from multiple hours to a few us/ns. Depending on the task to solve. There are different definitions of deadlines in real-time systems:

#### Hard deadline

A hard deadline is defined that the system has to deliver the correct results between a specified time interval. If the result is delivered too early or too late, serious harm can happen to the system or users. A typical example of a hard deadline is an airbag in a car.

#### Soft deadline

A soft deadline is defined that the results are delivered in average in the specified time interval. If the result is provided earlier or later in some cases, no consequences happen. An example might be a video stream application.

#### Firm deadline

No immediate harm happens if a deadline is missed, but the result of the job cannot be used in this interval. To achieve this goal a real-time system must run deterministically and predictable and needs to provide enough resources to serve the events correctly even though they arrive in high frequencies. In real-time applications, most commonly no operating system or a real-time operating system is used to ensure that the real-time jobs finish within their deadline requirements. The main difference between real-time operating systems and standard operating systems is that a less important task can be preempted immediately and high priority tasks are not delayed by other work that needs to be performed first. Further, the used platform requires to provide predictable access and execution times (worst case guarantees) on shared resources as, CPU, memory (cache, bus,

execution time

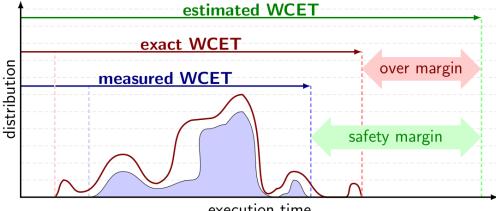

Figure 2.1: Estimation of the Worst-Case Execution Time, and the over-estimation problem [5]

memory controller), IO peripherals and other resources.

#### 2.1.1 **WCET**

To ensure that a job can fulfill a deadline requirement every time, it is necessary to retrieve its WCET. The WCET specifies the longest time a task takes to finish its assigned goal. To get the WCET of a program on a modern multiprocessor system, it is necessary to include all possible branches, used data and all possible contention with other active components in the system since no guarantee of exclusive execution can be given. This is done by measurement methods (start to end measurement with stressing benchmarks running in parallel) and static methods (instruction counting, detailed hardware model) [5]. Both approaches have their limitations, and an error margin needs to be taken into account. Especially since systems are getting more and more complex, it is difficult to estimate the error margin which leads to conservative WCET estimation and therefore low utilization of the system (see Figure 2.1).

#### Predicatbility problems in COTS 2.1.2

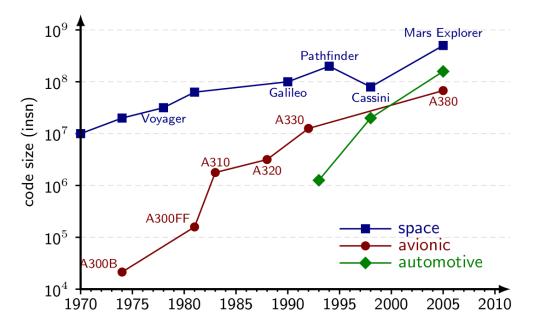

Today, it is more and more common to build real-time system using Commercial Off-The-Shelve (COTS) components, since computation demand on real-time systems increases (illustrated in Figure 2.2) and costs still need to be in a competitive range. These systems are designed to achieve high average throughput and perform therefore often much better than custom built real-time Hardware (HW) platforms. As a trade-off, the design did not consider worst-case timing guarantees required by real-time systems to ensure the hight average throughput. COTS systems often include optimizations as pipelining, out-of-order execution, data and branch speculation to parallelize instruction execution as much as possible in their cores. Additionally, they consist of multiple active components (CPU, IO-peripherals) that can independently initiate access to shared resources as the

Figure 2.2: Evolution of code size in space, avionic and automotive embedded systems [5]

main memory. In the worst case, this can lead to contention on communication buses, memory devices, and caches and therefore to degraded access times. Due to these optimizations, the WCET is estimated very pessimistically. As an example R. Pellizzoni et al.,2010 showed that the computation time of a task could increase linearly with the number of suffered cache misses due to contention in main memory. This means that if there are three active components in the system, the WCET can nearly triple.[6]

# 2.2 **PREM**

To cancel the contention problem and constantly achieve short and predictable response times for real-time task COTS components, it is necessary to control the operation-point of each shared resource and maintain it below saturation limits [3] to ensure no unpredictable processing delays occur. To tackle the contention on the level of bus communication and shared memory, the PRedictable Execution Model (PREM) is introduced [3]. Code of real-time tasks is analyzed and scheduled among all other active components in the system so that contention on accesses to shared resources is resolved and accesses to shared memory resources is scheduled without exceeding their saturation level. This means each task has exclusive access to the resources which allows a much more optimistic estimation of the WCET.

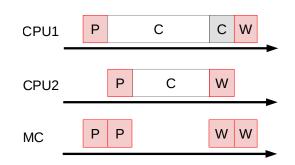

Figure 2.3: Predictable interval [1]

#### 2.2.1 Concept

To apply PREM, a real-time task is scheduled as a sequence of intervals of two different types: *predictable* and *compatible*.

#### Compatible interval

No transformations are performed for compatible intervals. During their executions, caches misses may happen any time, and the code is allowed to use OS calls. Compatible intervals can be preempted by interrupt handlers of associated peripherals. To reduce pessimism on the WCET, it is recommended to minimize the number of compatible intervals, and to keep them as short as possible. Therefore blocking calls performed within a compatible interval need to have some reasonable timeout.

#### Predictable interval

Predictable intervals are split into three phases: prefetch phase, compute phase, and writeback phase. The prefetch phase and writeback phase are also referred as memory phases. Figure 2.21 visualizes a predictable interval consisting of the mentioned phases. During the initial prefetch phase, the CPU accesses the main memory and prefetches the data used in the Compute phase into the last level cache. Since only one task in the system is allowed to be in a memory phase at once, no contention on the shared main memory happens. Since all the cache lines are already prefetched, the following execution of the compute phase experiences almost zero cache misses. Therefore the CPU which is currently running a compute phase does not access the main memory and another memory phases can be scheduled during this time. This allows the next predictable interval to enter its memory phase. To ensure that other active components in the system have enough time to perform their memory phases, the compute phase has a constant execution time. If it finishes earlier, it busy-waits until its deadline. At the end of a compute phase, another memory phase, called writeback phase, takes place to write back the memory. During the execution of a predictable interval, the CPU cannot be preempted by the OS or interrupt handlers.

#### PREM - transformation

To transform written code to PREM intervals, a particular compiler is used which is built on top of the LLVM Compiler infrastructure. The compiler is developed by ETHZ and is accessible under Hercules-public<sup>1</sup>. The compiler selects PREM-intervals and transforms them into the three phases *prefetch*, *compute* and *writeback*. First, the predictable interval is duplicated three times. On each instance of the duplicated code different transformations are applied that correspond to the single phases. [1]

#### Prefetch/Writeback

All instructions not related to memory access or calculating memory addresses, including control-flow, branches, and calculations are removed. Load instructions are replaced with prefetch instructions. After this transformation, the prefetch phase is reduced to its minimum. The writeback phase experiences a similar transformation, but load instructions are replaced with cache flush and invalidate instructions.[1]

#### Compute

The compute phase is taken as is. Since data is prefetched in the prefetch phase, these phases should not experience any cache misses during its execution. Except if the cache replacement policy has evicted some cache lines during the prefetch phase.[1]

#### PREM - scheduling

After the PREM intervals are determined and transformed, they need to be scheduled to meet the requirements specified by PREM. There are two possibilities to schedule the PREM phases: With an ordered schedule, which is computed offline or using an event-based schedule where each task tries to acquire a memory phase online and waits until no other tasks are in memory phase. The first approach was described and used by Joel Matějka et al. [1], where the gains of PREM have been shown nicely on the application of a GEneralized Matrix Multiplication (GEMM), a Fast Fourier Transform (FFT) and a binary search tree. This approach allowed to reduce the variance of completion times by the factor of 9 for optimal scheduling solutions and by the factor of 5 for scheduling solutions generated by use of a heuristic.

### 2.3 GPU introduction

In the early 1992 3D graphic cards were still very rare and a topic of scientific research and high-tech development. By the end of this decade, first 3D-graphic cards came to marked to fill this cap in personal computers. With the first graphic cards, the demand for video-games, advanced 3D-modeling in industry could be satisfied. The first available graphic cards on the marked were strictly

<sup>&</sup>lt;sup>1</sup>https://iis-git.ee.ethz.ch/H2020-Compiler/HerculesCompiler-public

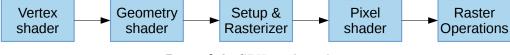

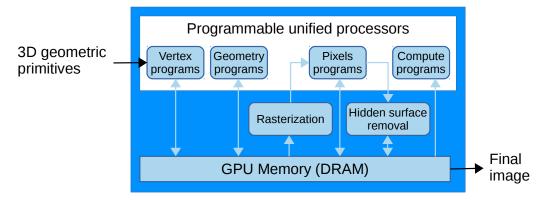

Figure 2.4: GPU rigid pipeline

designed to target the problem of 3D rendering and visualization. They had to output a rendered 3D model up to 60 times a second. Therefore they consisted of a rigid 3D-pipeline shown in figure 2.4. This pipeline consisted of five main stages: Vertex shader, Geomtry shader, Setup & Rasterizer, Pixel shader and Raster operation. The input was a 3D model of the scene using vertexes and edges and the output was a rendered 3D scene. In the first stage the vertexes of the model are manipulated (transformation, rotation, scaling) and vertex lightening is added, then the geometry shader removes hidden vertexes. In the pixel shader stage texture of colors and pixels is defined and added as pixel fragments. In the last stage those pixel fragments are rendered to pixels and aggregated to the final output image.[7]

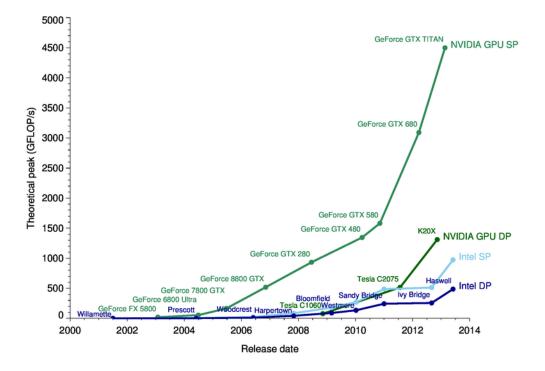

Later GPUs have evolved from the rigid hardware pipeline to a more multiple purpose implementation. Fixed function units have been transformed to a grid of unified processors (called Streaming Multiprocessor (SM) for NVIDIA hardware) that can perform those tasks and much more. This transformation has been done through the iteration of many GPU generations. This lead to the GPU-architecture presented in Figure 2.5 where the GPU consists of several general multiple purpose processors. This changes in the graphic pipeline opened completely new possibilities to use the GPU for different compute intensive tasks and not only for graphics related problems. Since in the last years the throughput and performance of GPUs (See Figure 2.6) has increased to a multiple of the performance offered by CPUs, industry and research use GPUs increasingly to parallelize compute intensive tasks. Due to the pipelined and parallelized architecture (Single Instruction Multiple Data (SIMD)), not all algorithms can efficiently utilize the cores of a GPU. Applications which are not well parallelizable and use incoherent and unpredictable memory accesses are not applicable to the streaming multiprocessors of a GPU. Compute intense tasks or streaming jobs on data sets map well to the GPUs streaming architecture. If the algorithms are chosen wisely the GPU can be used as a very efficient accelerator.[7]

#### 2.3.1 GPU on the Jetson TX2

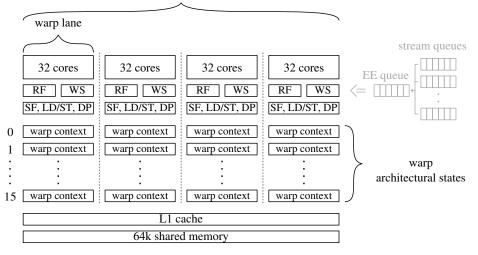

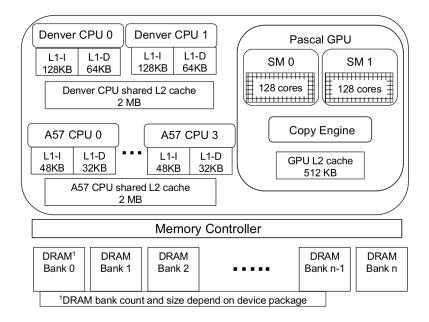

NVIDIA Tegra X2 is a high-performance embedded MPSoC consisting of two CPU clusters and one Pascal GPU with 256 CUDA cores. The memory bus is shared across the entire chip. However, each CPU cluster and GPU have a separate L2 cache. These caches are not coherent. The GPU is composed of two independent computing blocks called SM, Figure 2.7 shows a high level overview of such an SM in the of a GP100 Pascal GPU. In contrast to the GP100 GPU, the TX2 offers 128 CUDA-cores each having its L1 cache, instruction cache, shared memory, and four warp schedulers. For each warp scheduler the SM offers an instruction buffer, two dispatch units, a register file, 32 CUDA cores, 16 Double-Precision (DP)

**Figure 2.5:** "Graphics pipeline evolution. The NVIDIA GeForce 8800 GPU replaces the traditional graphics pipeline with a unified shader architecture in which vertices, triangles, and pixels recirculate through a set of programmable processors. The flexibility and computational power of these processors invites their use for general-purpose computing tasks." [7]

units, 8 Load/Store (LD/ST) units and 8 Special Function Units (SFUs) (sqrt, sin, cos...). Since one SM on the TX2 has 128 CUDA-cores and is partitioned into 4 warp schedulers, the threads are executed in groups of 32 threads, called a warp. If a workload is assigned to the SM the instructions are placed in the Instruction Cache. From there the workload is partitioned and distributed to the four warp schedulers Instruction Buffers. Unfortunately NVIDIA did not publicate how the partitioning is performed but it might be based on the assigned warp-id. The instructions in the Instruction Buffer are marked as ready if all dependencies are satisfied. The warp scheduler tries to fill both dispatch units with instructions marked as ready. Each cycle the warp scheduler gets the number of free Functional Units (FUs) and Dispatch Units. If there are not enough FUs available for the next ready instruction the warp-scheduler stalls or tries to issue another independent instruction to hide the latency. In the Dispatch Unit the warp-id is used to calculate the absolute address for each thread in the register file and the thread mask to decide which threads need to be executed in the next cycle. Then it sends the instruction to the free FUs. If not enough FUs are available the remaining instructions are queued for the next cycle and the dispatch unit remains busy for more than one cycle.

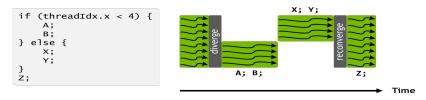

As previously mentioned the thread mask is used to mask the execution of threads for an instruction if they have diverged inside the warp. This happens if the warp has to execute a conditional branch as shown in Figure 2.8. In this case the first 4 threads take one branch and the other 4 threads the other branch. First, the thread mask is set to mask the latter 4 threads to execute the instructions A and B. If those threads reach the reconverge point the mask is inverted to mask the first 4 threads for the execution of instructions X and Y. After this point the unmasked execution takes place again for all threads to execute instruction Z [9]. This needs to be considered since this branching behaviour can reduce the parallelization in the GPU and nearly double the execution time in the worst case.

To visualize the warp-scheduling with more clarification, the Instruction Buffer can be imagined as a storage containing 16 warp contexts (instruction, warp id

Figure 2.6: CPU vs GPU performance[8]

and the thread mask). The warp scheduler checks if one of those warp contexts is ready and schedules on the designated warp lane or dispatch unit. Each warp lane executes a warp, i.e., a group of up to 32 threads performing the same instruction on different data. Since NVIDIA does not publish all details about their GPU architectures, it is difficult to estimate architecture details, and how GPU workload is scheduled on the available warp lanes. Based on publicly available documentation, previous work by Amert [10] and Capodieci [11], and our experiments, we assume the architecture of one streaming multiprocessor to be as depicted in Figure 2.9. The workload is inserted by CPUs into stream queues, then by rules revealed by Amert [10], put into the execution engine queue and assigned to an SM if enough resources are available. We assume that up to 16 warps can be assigned to a single warp lane. The warps from CUDA blocks are placed in the available *warp context* slots, which store their architectural state, and are run by the hardware warp scheduler (WS) as soon all dependencies of the threads are satisfied. The warp scheduler issues and interleaves instructions from the associated warps, hiding latencies caused by waiting for shared resources. After all warps in a block have finished, the occupied warp context slots are freed and can be reused by warps from the next block. Warp scheduling is similar to hyperthreading used in CPUs. Multiple running warps share CUDA cores and other resources such as multiple LD/ST units, SFUs and DP units in one warp lane. Latencies generated by instruction or data cache misses or other unsatisfied dependencies can be hidden by scheduling another warp-context. This way the GPU is busy as long there are enough threads ready to be executed.

Further the two SMs feature a shared nanosecond timer, called globaltimer, which runs synchronously on the GPU.

Figure 2.7: GP100 Pascal micro-architecture [9]

Figure 2.8: Diverged Warp execution [9]

TX2 streaming multiprocessor - 128 CUDA cores

Figure 2.9: Estimated architecture of one SM of TX2

# 2.4 CUDA

To allow an easy and straight forward implementation of computational work on the GPU NVIDIA introduced the CUDA framework <sup>1</sup>. To offload computation to the GPU, programmers write so called *kernels*, i.e., functions that execute in parallel on the GPU. When a kernel is launched the programmer specifies, with a special syntax, the kernel execution configuration: the number of threads and how those threads are organized into groups (CUDA-blocks or thread-blocks). Launched CUDA kernels are placed into queues called streams where they are executed in FIFO order. By default, there is one stream per process. More streams can be created to execute kernels in parallel if enough resources are available. All kernel launches are asynchronous, meaning that if a CPU needs to wait for kernel completion, it has to invoke explicit synchronization operation. A good starting point to familiarize with the CUDA framework is the CUDA C Best Practices Guide<sup>2</sup>.

#### 2.4.1 Programming model

The CUDA-Programming model splits a program into host and device code. Host code runs on the CPU and can only access data available on the CPU side. Device code on the other side runs on the GPU and can access data stored on the GPU. CUDA offers a framework to write programs that are able to run on both platforms. The code segment performing the transition of the execution from the CPU to the GPU is named kernel and can be called with a special syntax from the CPU side. To differentiate the code segments between host, kernel and device code CUDA offers two important keywords: \_\_global\_\_ and \_\_device\_\_. The \_\_global\_\_ keyword marks a function as kernel code. Those functions can be called from the CPU and issue a kernel launch on the GPU. The \_\_device\_ marks device functions. Those functions can not be called from the CPU but only from the GPU. Further this keyword allows to create global variables on the device accessible inside the running kernels.

Listing 2.1 shows the code of a simple CUDA program. First, the data is allocated and initialized on the CPU (host). Then, if the traditional memory model (see 2.4.2 Memory model) is used, memory is allocated on the GPU and the data is copied into this device environment using the GPUs copy engine. This data transfer step can be omitted sometimes if a different memory model is used. After the data is available on the GPU the kernel can be launched. To launch a kernel, the programmer specifies the number of threads to be used in the kernel and how those threads are grouped together into thread blocks. Further, the size of the used shared memory in a kernel and the stream, where the kernel launch is enqueued, can optionally be specified. Since all kernel launches are asynchronously, the programmer needs to place a cudaDeviceSychronize() call to issue an explicit synchronization before copying back the results. After the synchronization point the resulting data is copied back to the CPU and is available for further processing.

<sup>&</sup>lt;sup>1</sup>https://docs.nvidia.com/cuda/cuda-c-programming-guide/

<sup>&</sup>lt;sup>2</sup>https://docs.nvidia.com/cuda/cuda-c-best-practices-guide/index.html

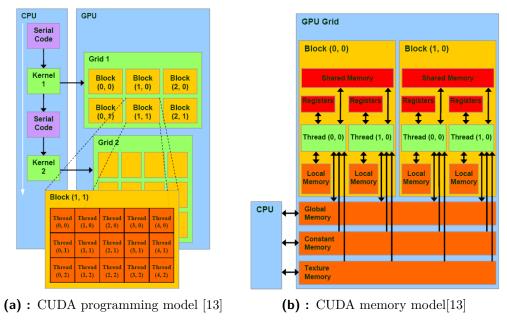

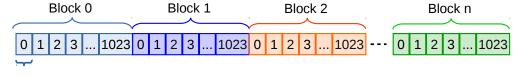

Figure 2.10a shows how a kernel is launched in a grid (collection of CUDAblocks) of thread blocks. The grid and the blocks can have up to 3 dimensions where each thread can be identified according to his X and Y block and thread ids, stored in the threadIdx.x, threadIdx.y, blockIdx.x, blockIdx.y registers.

During the kernel execution the thread and block ids indicate the running thread which element to access. If more elements need to be processed than threads are available the kernel implementation can be changed to use grid-stride loops to instruct threads to process more than one element.

Threads in one block can synchronize by use of barriers or communicate through the shared memory. One streaming multiprocessor can execute multiple blocks until some register, memory, thread limitations occur. But a CUDA block can not be split between two streaming multiprocessors since threads could not longer share their memory or synchronize.

The CUDA programming model has the disadvantage, that the offloading of algorithms to the GPU need some rewriting of the code. There are other possibilities, as for example OpenMP and OpenACC, to offload kernels by simple compiler directives. Those frameworks use the CUDA driver API behind the scenes and the algorithms are implicitly transformed to the CUDA language. Chapter 2.5 *OpenMP offloading* shows how GPU offloading using OpenMP works in more detail.

#### 2.4.2 Memory model

On the GPU, memory can be accessed in different locations. Figure 2.10b gives a short overview of the CUDA memory model. The red blocks represent fast, on-chip memory whereas the orange blocks represent slower memory. The registers are available per thread and CUDA-core and can be used for local storage. The second

```

Listing 2.1: Example kernel in CUDA: saxpy [12]

```

. . . . . . . . . . .

```

#include <stdio.h>

__global__ void saxpy(int n, float a, float *x, float *y)

ſ

int i = blockIdx.x*blockDim.x + threadIdx.x;

if (i < n) y[i] = a * x[i] + y[i];

}

int main(void)

{

int N = 1<<20;

float *x, *y, *d_x, *d_y;

x = (float*)malloc(N*sizeof(float));

y = (float*)malloc(N*sizeof(float));

cudaMalloc(&d_x, N*sizeof(float));

cudaMalloc(&d_y, N*sizeof(float));

for (int i = 0; i < N; i++) {</pre>

x[i] = 1.0f;

y[i] = 2.0f;

}

cudaMemcpy(d_x, x, N*sizeof(float), cudaMemcpyHostToDevice);

cudaMemcpy(d_y, y, N*sizeof(float), cudaMemcpyHostToDevice);

// Perform SAXPY on 1M elements

// kernel<<<gridDim, threadDim, sMem, stream>>>(ptr_data);

saxpy<<<(N+255)/256, 256>>>(N, 2.0f, d_x, d_y);

cudaDeviceSychronize()

cudaMemcpy(y, d_y, N*sizeof(float), cudaMemcpyDeviceToHost);

float maxError = 0.0f;

for (int i = 0; i < N; i++)</pre>

maxError = max(maxError, abs(y[i]-4.0f));

printf("Max error: %f\n", maxError);

cudaFree(d_x);

cudaFree(d_y);

free(x);

free(y);

}

```

on-chip memory is given by the shared memory (scratchpad memory) which gives the threads the possibility to communicate with each other and to exchange data since it is shared inside a CUDA-block. Further there is local, global, constant and texture memory. If data is loaded from global memory, data is by default cached in the L2 cache only. The L1 cache is only used for local memory to ensure that local data, which was stored in local memory due to register spilling, is not evicted by global loads cached in L1 cache. This behavior can be changed by the compiler flag -dlcm=ca to instruct NVIDIA CUDA Compiler (NVCC) that global loads should be cached in L1 cache.

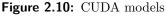

#### Traditional memory

In the traditional memory model the host and device manage separate memory locations. Before a kernel can process a dataset located in host memory, the programmer needs to allocate the memory on the GPU and issue a copy operation to copy the data to the GPU. After the kernel execution the resulting data needs to be copied back to the host.

To avoid a lot of copy operations, already allocated device memory can be reused to share memory between multiple kernels. This enables a more fine grained control about the data movement during the execution. The use of shared memory segments between multiple kernel calls is shown in Figure 2.11. It can be seen that matrix A is allocated in the device data environment. All kernels launches afterwards can access this data and work with it. The first kernel copies data B to the device environment and allocates D in it. Then it performs some work with AB and D. At the end of the kernel B and D are copied back to the host environment. The second kernel allocates C on the target and performs again with A and C. At the end C is copied to the host environment. This way the

Figure 2.12: TX2 block diagram[10]

copying of A can be avoided while different kernels can work on the same memory.

#### Zero-copy memory

As we can be seen in Figure 2.12, the Jetson TX2 platform shares memory between the CPUs and GPU. This enables to use host-pinned memory (not pageable) and unified managed memory in zerocopy mode. This means that the host CPU and GPU have pointers to the same memory location to work on data without the copy operations from host to device or vice-versa. Host pinned Zerocopy-memory retrieves a device pointer to a memory segment which is pinned to the CPU (not pageable). Using this device pointer the GPU can access the memory location. To ensure coherence of this memory location caches are disabled which lead to a significant slowdown in performance. The unified managed memory model offers an abstraction layer to the memory access. Memory is allocated in the unified memory space and therefore in host and device memory. The Unified memory model ensures the consistency between those two memory location behind the scenes using page on demand technology. For the programmer point of few its seems to work with only one pointer on the GPU and CPU without explicit copy operations to the device and back. Since the Jetson TX2 platform offers shared memory, the unified memory model allocates the memory segment only once and uses therefore also Zerocopy-memory but this time with caches enabled. This has the advantage of a speed up compared to the host pinned Zerocopy-memory but needs cache flushes to ensure synchronization between CPU and GPU caches and can induce some unpredictable overhead on page misses, since some CPU interaction is need to resolve the page miss. Listing 2.2 shows the calls to allocate host-pinned and managed unified memory segments.

Listing 2.2: Host pinned zero copy memory

#### 2.4.3 Coalescent access

In a kernel launched on the GPU, multiple threads might work in parallel and access memory in parallel. Therefore it would be desirable that the access to memory of the single threads are not evicting already cached memory of other threads. This can be achieved by using a as coalescent memory access as possible.Figure 2.13, shows an access pattern where each block processes 1024 consecutive elements in memory. This leads to a fast and efficient access since the thread in one block have less competition for memory. If a coalescent access to the data in global memory can not be provided a solution can be to copy a memory segment into the shared memory of the block to provide a coalescent during the further computations.

Index = Block id \* num\_threads + thread id

Figure 2.13: Coalescent memory access

## 2.5 OpenMP offloading

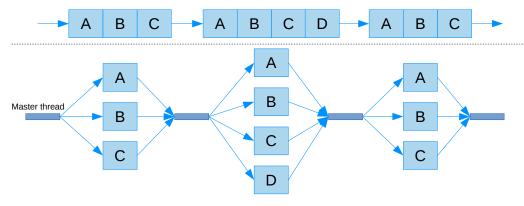

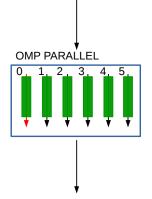

OpenMP (Open Multi-Processing) is an API that supports multi-platform shared memory multiprocessing programming in C, C++, and Fortran. It consists of a set of compiler directives, library routines, and environment variables that influence run-time behavior. OpenMP uses a portable and scalable model that gives programmers a simple and flexible interface for developing parallel applications for platforms ranging from the standard desktop computer to the supercomputer. It is a multi-threading implementation which instructs a master thread to fork the code segment to a specified number of slave threads (See 2.14).

Figure 2.14: OpenMP model

To parallelize a section of code, for example a for loop, it is marked with appropriate compiler directives to specify how to distribute it along the slave threads. Each thread has its unique id starting at 1, whereas the master thread has the id 0. By default each slave thread executes the code by its own. Using work sharing constructs allows to distribute the workload along the available slave threads so each thread performs its particular piece of work. An easy example how the parallelization work, is shown in listing 2.3. Here a parallel region is executed once by each launched thread. Each thread prints out its assigned id. For the master thread it is id 0 and for the slave threads the incremented number starting from 1. The threads can use the OpenMP runtime library to retrieve their id during the execution. In this example the call to omp get thread num() was used. Listing 2.4 shows an example how a for loop is parallelized using openMP. The workload is distributed by OpenMP along the optimal number of threads, which is usually the number of available cores in the system. In more detail, the omp parallel clause marks the for loop as a parallel region and the omp for clause instructs the compiler to distribute the work along the available threads. The omp schedule directive defines to use a static schedule with chunk size 1. Therefore each thread processes one element per iteration. If the chuck size would be bigger, for example 10, each thread would perform 10 iterations until it is free for the next 10 elements. Since the omp nowait clause was not used, the threads wait at the end of the parallel region until every thread has finished. Therefore a implicit barrier is generated.

Listing 2.3: OpenMP Hello World!

```

int main(int argc, char* argv[]) {

#pragma omp parallel

{

int ID = omp_get_thread_num();

printf("Hello World from core: %d\n", ID);

}

return 0;

}

```

Listing 2.4: OpenMP example on CPU

```

void foo(int n, float *a, float *b) {

#pragma omp parallel for \

schedule(static, 1)

for (int i=1; i<n; i++){

b[i] = (a[i] + a[i-1]) / 2.0;

}

}</pre>

```

#### 2.5.1 Offloading kernels

To instruct OpenMP to offload a kernel the omp target clause is needed. This clause generates a target region which copies data to the target environment executes the kernel and copies the results back. This section describes the offloading process on the generalized matrix multiplication of Polybench-C. Listing 2.5 shows the offloaded kernel.

Listing 2.5: GEMM - sequential c

```

for (int i = 0; i < NX; i++){

for (int j = 0; j < NY; j++){

C[i][j] *= beta;

for (int k = 0; k < NZ; ++k)

C[i][j] += alpha * A[i][k] * B[k][j];

}

}</pre>

```

### Simple offloading

With the omp target clause the offloading to the target is triggered as shown in listing 2.6. Each target region is also a data region which means that data used

in the kernel is mapped to the device. If not specified with the omp target map clause, data is mapped using the *tofrom* classifier. This means, data is copied to the device before the kernel execution and copied back after the kernel execution. This does not necessarily apply to constant variables since they can be used as absolute values. Since no omp target teams clause was used, the compiler generates one team (CUDA-block) whose master thread executes the parallel region. The omp parallel for (thread\_limit) launches the slave threads on the device and distributes the work along them. If the number of threads is not defined the maximum number allowed per CUDA-block is used.

#### Listing 2.6: GEMM - simple offloading

#### Teams and Threads

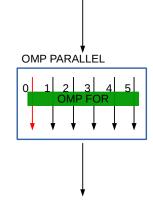

This subsection describes the parallelization and work sharing constructs omp parallel, omp teams, omp for and omp distribute working with teams and threads. These OpenMP clauses can be combined to instruct how the workload should be distributed and to achieve as much parallelism as possible. In OpenMP, the threads are launched in teams. An OpenMP team corresponds to a CUDA block. The omp parallel clause launches a team of slave threads, where each slave thread executes the same parallel region (See Figure 2.15a). To distribute the code of a parallel region along the slave threads the clause omp for clause can be used. This clause instructs the compiler to split the parallel region, in this case a for loop, into multiple chunks and assigns those chunks to the slave threads (See Figure 2.15b). The chunk size and the schedule which are assigned to the threads can be specified using the clause omp schedule(type,chunk size).

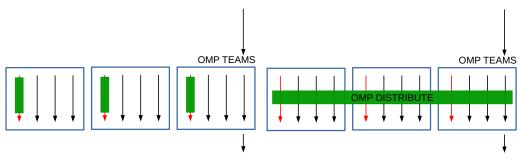

Since GPUs can hide latencies if multiple thread blocks are executing concurrently it is desirable to distribute the parallel work also across multiple teams. This is done in CUDA using the concept of grid and blocks. This is solved similarly in OpenMP using the omp teams directive which launches multiple teams of threads (CUDA-blocks). As shown in Figure refpic:openmpteams multiple teams are launched but each master thread of the teams executes the same region of code. Therefore the omp teams distribute clause is needed to distribute the

(a) : omp parallel launches team of threads where each thread executes the same parallel region.

(b): omp parallel for distributes the work load across the threads in a team

Figure 2.15: OpenMP parallel launch

(a) : omp teams launches a league of teams, where the master threads of the teams execute the same parallel region

(b) : omp teams distribute launches a league of teams and distributes the workload along the master threads. The distribution within the teams is not specified yet and needs further work sharing constructs as omp parallel for

Figure 2.16: OpenMP teams launch

region along the teams (Figure 2.16b). But there is still the problem, that only the master threads of the teams are executing the assigned region. Therefore the omp teams distribute needs to be combined with omp parallel for to achieve also full parallelism within the teams. It is important to note, that there is no synchronization between the teams.

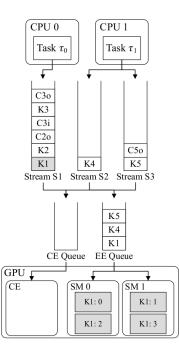

## **2.6** GPU scheduling on the TX2

As described previously, the CUDA kernels are executed in multiple blocks consisting of several threads. Those blocks are assigned to the SMs if enough resources are available and the warp scheduler, which is implemented in hardware, swaps warps immediately if stalls (example waiting for memory) in a running warp occur. This way memory latencies can be hidden and the SM is fully utilized. This scheduling is done in hardware and can not directly be influenced by the programmer. CUDA offers streams to order GPU operations. Operations in a stream are executed in FIFO order, but the order along different streams is determined by the GPU scheduling policy. It is possible to assign priorities to the streams to prioritize the execution of certain streams. Therefore kernels from multiple streams may execute congruently or out of launch time order. The rules the GPU uses to schedule blocks originating from different streams is not well documented, but Tanya Amert et al. have revealed some restrictions with different experiments [10]. Their research considers multiple running instances of synthetic benchmarks with different configuration of block resource requirements, kernel durations and copy operations. Further they assume several queues where kernel and copy operations are enqueued:

- Execution engine queue (EEQ): Queue which holds blocks to be assigned to a SM (FIFO)

- Copy engine queue (CEQ): Queue which holds copy operations to be assigned to copy engine (FIFO)

- One FIFO queue per CUDA stream.

Figure 2.17 shows the assumed queue architecture. Generally said, the head of all stream queues is placed in FIFO order in the EEQ. Only the blocks of the kernel placed at the head of the EEQ can be assigned to the SMs if enough recourses are available. If all blocks of a kernel are assigned, this kernel is removed from the EEQ. After all blocks of a kernel have completely finished their execution on the SMs, the kernel is also removed from its stream queue. Then the next kernel from the stream queue can be placed in the EEQ. This rules, discovered by Tanya Amert et al.[10], can help a programmer to implement and tune a CUDA application to be scheduled the way as expected.

Figure 2.17: TX2 queue architecture [10]

# 2.7 Related work

Similarly to our work, recent research by Cavicchioli et al. characterized interference on main memory and communication bus level between the CPU and GPU [14]. Other researchers [15, 16] developed various microbenchmarks to understand GPUs and their memory system. Our work differs from those by using time triggered scheduling.

The scheduling behavior of many GPUs is unknown in most cases due to a lack of publicly available and open documentation. Therefore, GPUs are mostly treated as a black boxes, and different approaches for predictable execution of different workloads have been developed to bypass this uncertainty. An often used method is to ensure that only one process can access the GPU resources at a time by use of a locking mechanism [17]. The cost of this approach may be an underutilization of powerful GPUs. Dividing the workload into smaller preemptable chunks could reduce this problem [18, 19]. Others evaluated techniques to manage accesses to memory [20] to reduce contention between GPU and CPU applications.

Further Otternes et al. assessed the NVIDIA TX1 platform regarding real-time behavior concerning co-scheduling of multiple kernels [18][19], and additionally, Amert et al. derived a set of the GPU scheduling rules used in the Jetson TX1 and TX2 platforms to brighten up the black box nature of those platforms [10]. They ran different experiments to understand how the GPU schedules work if submitted from the same or different processes. They found that the GPU workload launched from different processes shares the GPU by the use of multiprogramming, where each kernel runs exclusively on the GPU during its assigned time slice and does

| $\sim$ | Packground |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|--------|------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|

| Ζ.     | Background |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|        |            |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

not overlap other GPU computation. For GPU workload submitted from the same process, the computation can overlap and is scheduled according to the derived rules. Bakita et al. proposed a validation framework to validate those derived rules for future GPU generations [21].

Capodieci et al. [11] changed how the GPU workload is scheduled by using an EDF scheduler combined with a Constant Bandwidth Server. Their scheduler is implemented in a hypervisor and works by replacing the run list inside the GPU-host.

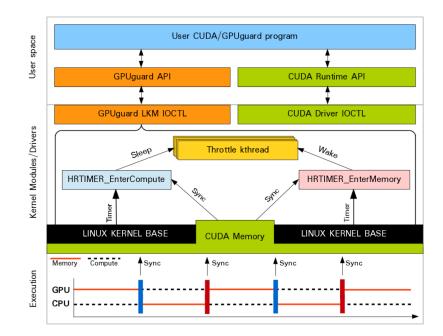

### 2.7.1 GPU-GUARD

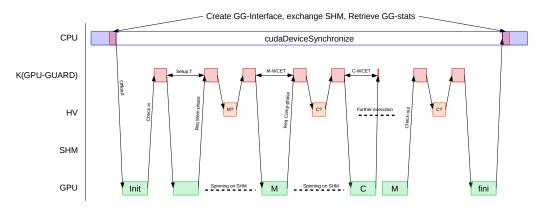

To adapt the GPU execution to the Predictable execution model, the kernels are also premized similar to the CPU premization mentioned in the previous chapter 2.2 by use of the Hercules compiler [22]. Therefore kernels are separated into the *Memory* and *Compute* phases. Really short kernels which are not usefully premizable are hold as is and treated as *Memory* phases. The other kernels are tiled into loop segments only accessing data segments of the size of 48kBytes. This size comes from the limitation that each thread block can use up to 48kBytes of shared memory called scratch pad memory. In the following compute phases the running threads can access their data in the scratchpad memory (shared memory) without further memory misses. To synchronize the PREM phases with PREM phases running on the host, the tool GPU-Guard was introduced by Björn Forsberg et al. [20]. Figure 2.18 shows the initial architecture of GPU-Guard. It consists of the CUDA/GPUguard program and the GPUguard Loadable Kernel Module (LKM). Since the only way to communicate between the GPU and CPU on the Jetson TX2 platform is through main memory, the communication between the LKM and the kernel on the GPU is based on polling on a host pinned memory location. Each thread block in the CUDA code writes to its shared memory location to indicate that it wants to enter a new PREM phase. Then it is busy waiting on this location until the request is acknowledged by the GPU-guard LKM. In the beginning of a CUDA-kernel execution each thread block performs a checks in request to GPUguard. This way GPUguard knows how many CUDA blocks belong to a single kernel. The same happens at the end of a CUDA-kernel where each thread block requests a checks out. After all CUDA blocks performed a successful checkout, GPUguard knows that the kernel has finished and is ready to synchronize the next kernel. After all blocks have checked in, the single blocks acquire a memory phase and busy wait on their shared memory locations until it is acknowledged. GPUguard on the other side only acknowledges the Enter memory *phase* request after all running blocks have requested it. The same happens on the request *Enter compute phase*. This way it is ensured that all blocks running on the SM congruently are entering a memory phase the same time. Therefore the whole GPU (all running block on the GPU) is either in *memory phase* or *compute* phase. This process is illustrated in Figure 2.19.

The GPUguard LKM consist of a high resolution timer callback function and throttle threads. After the GPU was allowed to enter a memory phase, the throttle threads are launched on all cores to throttle down the CPU execution. This way it is ensured, that the CPU is not accessing the communication bus or the memory.

Figure 2.18: An architectural overview of the implemented GPUguard. [20]

To enable a real synchronization with the PREM applications on the host, those throttling threads were replaced with call to Memguard to acquire a memory phase. This call is blocking until a new Memory phase slot is available. In this case GPUguard acknowledges the GPU *Enter memory phase* and the GPU enters the memory phase. On a *Enter compute phase* request on the other hand the lock in Memguard is returned, so other PREM tasks can enter their memory phases. This is also done after all blocks have checked out, to ensure that the GPU gives back the memory lock also for shorter not premized kernels (treated as memory phase). To enable the integration of the MEMguard call, some modification to the reloading of the high resolution timer had to be made. Since the call to the hypervisor is blocking, this time needs to be added to the newly configured WCET interval.

The high resolution timer is used to ensure that the GPU kernel do not overrun their given memory and compute phase times. After acknowledging the *Enter memory phase* request of the GPU the high resolution timer is configured to overrun after the estimated memory WCET time. If the running block did not request a *Enter compute phase* after the high resolution timer has fired, a memory phase overrun is detected. If a request was detected, the timer is updated with the estimated compute WCET. Again, if no phase change request was detected after the timer has fired, a compute overrun is detected. The detected overruns are returned at the end of the kernel execution and can be used to tune the WCET values for the kernel. Those values are not determined per phase, but per kernel, since constant memory phase and compute phase times are expected. After no more overruns are detected, the estimated values can be used for a correct synchronization between the host and GPU PREM tasks.

Figure 2.19: GPU-guard synchronization with HV

This way of PREM synchronization between the host and GPU introduces two main causes of overhead: First the shared memory communication is rather slow, since caches are disabled on host-pinned shared memory. But communication cannot be performed in other ways, this over head is not reducible. Secondly the WCET times are estimated over multiple runs (up to several 1000 if starting of WCET=100ns and adding 100ns on each detected overrun) of the kernel. This leads to a pessimistically estimated WCET and kernels that perform faster than the configured WCET time in the high resolution timer have to spin until this interval has expired. This could be reduced by using a higher sampling rate in the LKM to detect earlier finishes in the phases and acknowledging faster phases change requests.

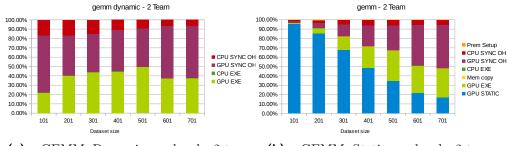

### 2.7.2 PREM-Synchronization with GPUguard

During the individual project we made some measurements to evaluate the synchronization overhead induced by the premization with the Hercules compiler and the synchronization with GPUguard. To measure this overhead we instrumented the premized executable to retrieve the times the program spends in the phases presented in table 2.1.

- CPU-time: Total execution time kernel (including memcopy) time

- GPU-time: Using nvprof kernel execution time

- Premized time: Time collected using binary which is premized by Hercules

- Notpremized time: Time collected using binary which was not premized by Hercules

Figures 2.20a and 2.20b show how much time an executable spends in the single phases compared to the total execution time. It can be seen, that the dynamic synchronization overhead is always around 50% which degrades the performance significantly. This delay is mostly induced due to the slow communication through the shared main memory.

| Name                     | Desribtion                                                       | Measurement method                                      |

|--------------------------|------------------------------------------------------------------|---------------------------------------------------------|

| PREM setup               | Time spend to setup<br>PREM environment                          | In libpremnotify                                        |

| CPU Sync over-<br>head   | PREM synchronization<br>overhead introduced on<br>CPU            | Premized CPU time minus CPU<br>time without premization |

| GPU sync over-<br>head   | PREM synchornization<br>overhead introduced on<br>GPU            | Premized GPU time minus CPU<br>time without premization |

| CPU execution            | CPU execution without premization                                | Notpremized execution totaltime<br>minus kernel time    |

| Memcopy                  | Memcopy operations                                               | Using nvprof                                            |

| GPU execution            | GPU kernel execution<br>without premization<br>(run target team) | Notpremized execution<br>nvprof(run target team)        |

| GPU static over-<br>head | Static GPU overhead<br>(init device and load bi-<br>nary)        | nvprof                                                  |

Table 2.1: Measured execution phases

(a) : GEMM: Dynamic overhead - 2 team (b) : GEMM: Static overhead - 2 team

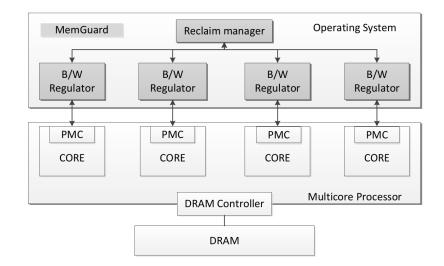

### 2.7.3 Mem-guard

Memguard was introduced by Heechul Yun et al. [23]. It is used to provide isolation between PREM tasks during their memory phases. PREM tasks request Memguard to enter a memory phase. With this requests Memguard ensures that only one task on the system can enter a memory phase at a time. After the request is granted, Memguard monitors the memory usage of the running task using performance counters. If a core outruns its assigned memory budget the corresponding jobs is preempted and put to sleep. After a preset time instance the memory budget is renewed and the task is allowed to run further. Thanks to the use of performance counters, only cache misses are detected. Therefore a task is allowed to run further if it keeps hitting into is local cache. Memguard consists of two main parts, the per core regulator and the reclaim manager. The

monitoring of the memory usage and throttling of the running tasks is done in the per core regulator and the reclaim manager is responsible to maintain the global shared reservation (receiving and re-distribution) of the memory budget for all regulators in the system[23].

Figure 2.21: MemGuard system architecture. [23]

## Chapter 3 Methodology

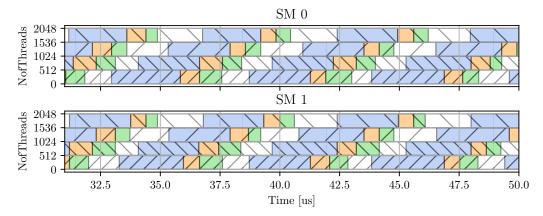

In this section, we present the used synchronization mechanisms and benchmarks. We ran all experiments on the Jetson TX2 in NV Power Mode MAXN and with all frequencies configured to the maximum values by running *jetsonclock.sh*<sup>1</sup> in order to get reproducible results. The TX2 was flashed with the Jetpack versions 3.1 (CUDA-8) and 3.3 (CUDA-9). First, we performed different artificial experiments based on sequential and random walks to analyze the caches on the GPU and their behaviour. We ran the walks in different kernel and thread configurations to characterize the interference on memory accesses. Later, we evaluated the possible synchronization mechanisms to schedule the PREM phases on the GPU, and then we measured the kernel to kernel interference based on a 2D Convolution example. To reduce the interference and therefore the induced execution jitter, we tiled the 2D Convolution into the PREM phases and scheduled the single tiles with the globaltimer available on both SMs. Table 3.1 gives a short overview of selected parameters describing the target platform.

| Parameter   | Value                         |

|-------------|-------------------------------|

| OS          | Ubuntu 16.04                  |

| Jetpack     | 3.1 and 3.3                   |

| Main memory | $8  \mathrm{GB}$              |

| CPU         | NVIDIA Denver2 (dual-core)    |

|             | ARM Cortex-A57 (quad-core)    |

| GPU         | Pascal (2 SMs with 128 cores) |

Table 3.1: Technical specification of the TX2

## **3.1** Platform characterization

In this section, we describe the used experimental setup to evaluate the cache sizes and the contention between the running threads on the TX2. All the experiments are based on random and sequential walks performing read-only accesses on a

<sup>&</sup>lt;sup>1</sup>Script provided by NVIDIA to configure board clocks

3. Methodology

shared array. During the walks, each thread records the average element access time. For these experiments, we evaluated the change of the average access time in function of the used dataset size, the number of congruently running threads and kernels, and induced interference from the CPUs.

#### 3.1.1 SASS

Independent of the used time source to measure the average element access time, it is crucial to know how the instrumented code segment executes and that it includes the desired instructions. To allow the extensive parallelize on the GPU, NVIDIA had to relax the rules for data coherence and dependencies to allow a more radical reordering of instructions. This can lead to the problem that code segments we would like to measure can be moved out of the instrumented code region. To ensure that the measurement is performed correctly, one has to inspect the assembly output of the NVCC.

To compile a CUDA program with NVCC, the programmer has to specify the real and virtual target architecture. The virtual architecture (ex. compute\_62) instructs NVCC to generate the Parallel Thread Execution (PTX) Assembly for this architecture. The PTX assembly can be seen as an intermediate, assembly-like representation of the CUDA kernels and is not heavily reordered yet. The compiler optimizes and assembles the PTX code for the target architecture if the programmer passes the real architecture parameter (ex. sm\_62). In this step, heavy reordering and loop unrolling take place to optimize the executable for the target architecture. These optimizations are performed in different ways and with different results from CUDA version to CUDA version. Therefore it is important to inspect the resulting binary. NVIDIA provides the useful program cuobjdump -sass prog which shows the passed binary content in the form of a Streaming ASSembly (SASS) output. SASS is a human-readable output which allows the programmer to understand the order of the issued instructions.

To visualize to reordering problem we have a look at the simple kernel code shown in listing 3.1. At the beginning of the kernel, the current cycle counter value is read and stored into the variable temp1. Then a for loop is executed to fill in the data\_clock array. After this for loop, the cycle counter is reread and stored in variable temp2. In the end, the two retrieved values are subtracted to get the total amount of cycles consumed by the for loop and is stored in global memory.

We compile this kernel now for the architecture of the TX2. Once by use of CUDA 8 (Listing 3.2) and once with CUDA 9 (Listing 3.3). On first sight, the shown SASS output seems to be similar between the two versions. For sure we have the same amount of instructions, but if we have a closer look, we see that the reordering took place differently. For the instructions filling the array in the for loop, this is not a problem, since we still have the same result. However, the problem lies with the retrieval of the cycle counts performed with the CS2R Rx, SR\_CLOCKLO calls. In the example compiled with CUDA-8 we can see that the compiler reordered the code heavily and placed the two SR\_CLOCKLO calls to the beginning of the kernel. This leads to the problem that the consumed cycles by the for loop are not recorded at all. With CUDA-9 on the other hand, the SR\_CLOCKLO have not been reordered and the measurement takes place correctly.

Listing 3.1: Simple kernel for SASS generation

.

```

#define DSIZE 4

__global__ void kernel(unsigned int*data_clock){

unsigned int temp1, temp2;

temp1 = clock();

for ( int i = 0; i< DSIZE; i++){

data_clock[i] = i;

}

temp2 = clock();

data_clock[0] = temp2 - temp1;

}</pre>

```

This example shows that it is essential to inspect the instrumented kernels to ensure that we measure the desired pieces of code. To have the same result with both CUDA versions in this example. It is sufficient to pass DSIZE as a kernel parameter so the for loop cannot be unrolled that extremely by the compiler.

| Listing 3.2: | CUDA-8 SASS generation | Listing 3.3: | CUDA-9 SASS generation  |

|--------------|------------------------|--------------|-------------------------|

| /*0008*/     | MOV R1, c[0x0][0x20];  | /*0008*/     | MOV R1, c[0x0][0x20];   |

| /*0010*/     | MOV RO, c[0x0][0x140]; | /*0010*/     | CS2R RO, SR_CLOCKLO;    |

| /*0018*/     | CS2R R5, SR_CLOCKLO;   | /*0018*/     | MOV R2, c[0x0][0x140];  |

| /*0028*/     | IADD32I R2.CC, R0, 0x4 | ;/*0028*/    | IADD32I R2.CC, R2, 0x4; |

| /*0030*/     | CS2R RO, SR_CLOCKLO;   | /*0030*/     | MOV32I R4, Ox1;         |

| /*0038*/     | MOV32I R4, Ox1;        | /*0038*/     | MOV32I R5, Ox3;         |

| /*0048*/     | MOV32I R7, 0x2;        | /*0048*/     | MOV32I R7, 0x2;         |

| /*0050*/     | IADD.X R3, RZ, \       | /*0050*/     | IADD.X R3, RZ, \        |

|              | c[0x0][0x144];         |              | c[0x0][0x144];          |

| /*0058*/ {   | IADD RO, -RO, R5;      | /*0058*/     | STG.E [R2], R4;         |

| /*0068*/     | STG.E [R2], R4; }      |              |                         |

|              |                        | /*0068*/     | STG.E [R2+0x8], R5;     |

| /*0070*/ {   | MOV32I R5, 0x3;        | /*0070*/     | STG.E [R2+0x4], R7;     |

| /*0078*/     | STG.E [R2+-0x4], RZ; } | /*0078*/     | STG.E [R2+-0x4], RZ;    |

| /*0088*/     | STG.E [R2+0x8], R5;    | /*0088*/     | CS2R R5, SR_CLOCKLO;    |

| /*0090*/     | STG.E [R2+0x4], R7;    | /*0090*/     | IADD RO, -RO, R5;       |

| /*0098*/     | STG.E [R2+-0x4], R0;   | /*0098*/     | STG.E [R2+-0x4], R0;    |

| /*00a8*/     | EXIT;                  | /*00a8*/     | NOP;                    |

| /*00Ъ0*/     | BRA OxbO;              | /*00Ъ0*/     | EXIT;                   |

| /*00b8*/     | NOP;                   | /*00Ъ8*/     | BRA Oxb8;               |

#### 3.1.2 Measurement overhead

To retrieve the time a program spends in a kernel CUDA offers three time sources: clock(), clock64() and the globaltimer. To see how much overhead is induced by the single measurement methods, we run a simple experiment that calls each time source two times and measures the time between the two subsequent calls. Depending on the used measurement method in the following experiments, we subtract this measurement overhead from the results. Table 3.2 shows the measured overhead. For the two clock sources, we did not measure the time of the call with the globaltimer. Therefore no information regarding the call duration in nanoseconds is available. The difference in nanoseconds between two subsequent calls to read the globaltimer ranges between 0 and 128 ns. This is due to the resolution of the globaltimer and exhibits the limitations that the globaltimer can only be used for bigger code segments.

| Time source | Overhead in Cycles | Overhead [ns] |

|-------------|--------------------|---------------|

| clock()     | 6                  | -             |

| clock64()   | 55                 | -             |

| globaltimer | -                  | 0-128         |

Table 3.2:

Measurement overhead

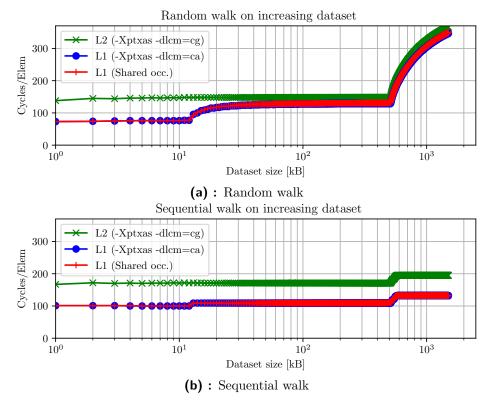

#### 3.1.3 Cache analysis

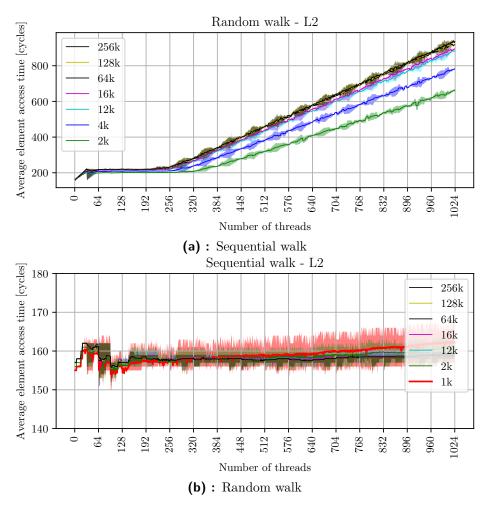

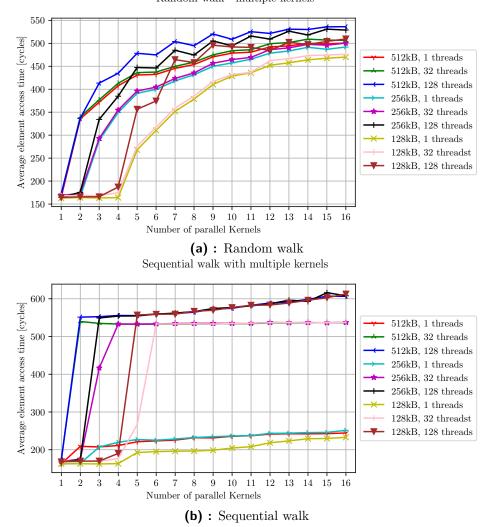

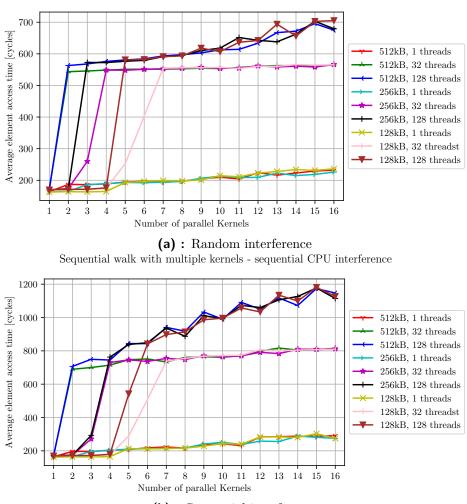

To analyze the available caches and their size on the TX2, we launched a kernel to perform a random, respectively a sequential, walk on differently sized datasets. We launched the kernels with one CUDA-block consisting of one thread to ensure that no competition on memory occurs during the walk. Listing 3.4 shows how the kernel performs the walk. We used the clock64() function to retrieve the cycle count to avoid overflows of the 32bit cycle counter in the case of bigger datasets. For the two walks, we allocate an integer (4bytes) array of the desired length and fill each element with its index of the next element to create a closed loop. For the random walk, this linked list is shuffled to create one closed random loop.